Overview

Fault Tolerance in Safety Critical Applications

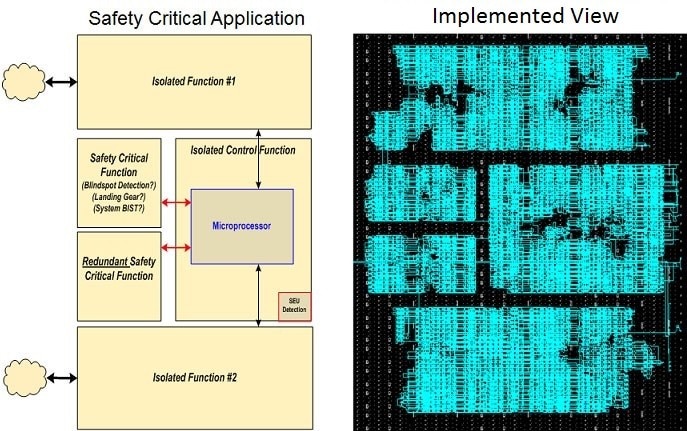

The ability to control system failure modes through fault-tolerant design requires an implementation methodology that ensures fault propagation can be controlled. AMD Isolation Design Flow (IDF) provides fault containment at the FPGA module level, enabling single-chip fault tolerance by various techniques including:

- Modular redundancy

- Watchdog alarms

- Segregation by safety level

- Isolation of test logic for safe removal

IDF, pioneered for government cryptographic systems, is also appropriate for avionics, functional safety-related electronics, industrial robotics, critical infrastructure, financial systems, and other high-assurance, high-availability, and high-reliability systems. The IDF is part of a spectrum of reliability technologies that when appropriately combined provide unmatched reliability, performance, and cost effectiveness.

In addition to its long heritage serving government grade cryptographic systems, the IDF is an integral part of the AMD IEC61508 (Industrial Functional Safety) certified tool chain. Additionally, it can aid in meeting the requirements of the ISO26262 specification (Automotive Functional Safety).

Device and Software Support

| Device | Supported Software |

| Virtex™ 4 | Existing Programs Only |

| Virtex 5 | ISE™ 14.7 |

| Spartan™ 6 (LX75/75T, LX150/150T) | ISE 14.7 |

| Artix™ 7, Kintex™ 7, Virtex 7, Zynq™ 7000 | ISE 14.7 / Vivado™ 2015.x or newer |

| UltraScale+™ & Zynq UltraScale+ | Vivado 2018.3 or newer |

| Spartan 7* | Vivado 2018.3 or newer |

* Only 7S50

IDF Methodology

IDF is a methodology based on existing implementation tool flows (ISE design tools in this case). Additional time spent floor-planning the design is done using existing constraint tools (PlanAhead / Vivado GUI). Verification of work products (pinout and routed design) are done with a separate and independent tool (either IVT or VIV for ISE or Vivado respectively).

Documentation and Reference Designs

Virtex 5 FPGAs

- Single Chip Cryptography (SCC) for Virtex 5

The Developing Secure Designs Using the Virtex 5 Family (XAPP1134) application note and reference design helps FPGA designers implement the AMD Isolation Design Flow for Fault-Tolerant Systems SCC technology.

- SCC Using ISE 11.4 / 11.5 Design Suite

The Single Chip Crypto Lab Using PR/ISO Flow with the Virtex 5 Family (XAPP1135) application note and reference design helps FPGA designers implement the AMD Isolation Design Flow for Fault-Tolerant Systems SCC technology using ISE 11.4 / 11.5 Design Suite.

- SCC Using ISE 12.1 / 12.4 Design Suite

The Single Chip Crypto Lab Using PR/ISO Flow with the Virtex 5 Family for ISE Design Suite 12.1 (XAPP1105) application note and reference design helps FPGA designers implement the AMD Isolation Design Flow for Fault-Tolerant Systems SCC technology using ISE 12.1 / 12.4 Design Suite.

Spartan 6 FPGAs

- Isolation Design Flow (IDF) for Spartan 6

The Developing Secure Designs with the Spartan 6 Family Using the Isolation Design Flow (XAPP1145) application note and reference design helps FPGA designers implement safe and secure designs.

- Isolation Design Flow Lab Using ISE 12.4 Design Suite

The Implementation of a Fail-Safe Design in the Spartan 6 Family Using ISE Design Suite 12.4 (XAPP1104) application note and reference design helps FPGA designers use the Isolation Design Flow by implementing a secure design.

7 Series FPGAs

ISE Design Suite

- Isolation Design Flow (IDF) Rules/Guidelines for 7 Series

The Isolation Design Flow for AMD 7 Series FPGAs or Zynq 7000 AP SoCs (XAPP1086) application note and reference design helps FPGA designers implement safe and secure designs for fault-tolerant systems.

- Kintex 7: Isolation Design Flow (IDF) Lab Using ISE 14.4 Design Suite

The 7 Series Isolation Design Flow Lab Using ISE Design Suite 14.4 (XAPP1085) application note and reference design helps FPGA designers use the Isolation Design Flow by implementing a secure design.

Vivado Design Suite

- Isolation Design Flow (IDF) Rules/Guidelines for 7 Series (Vivado Tools)

The Isolation Design Flow for AMD 7 Series FPGAs or Zynq 7000 SoCs (Vivado Tools) (XAPP1222) application note and reference design helps FPGA designers implement safe and secure designs.

- Zynq 7000: Vivado Isolation Design Flow (IDF) Lab

The Zynq 7000 SoCs or 7 Series FPGAs Isolation Design Flow Lab (Vivado Design Suite) (XAPP1256) application note and reference design helps FPGA designers use the Isolation Design Flow by implementing a secure design.

UltraScale+ FPGAs & Zynq UltraScale+ MPSoC

Vivado Design Suite

- Isolation Design Flow (IDF) Rules/Guidelines for UltraScale+ FPGA

The Isolation Design Flow for Zynq UltraScale+ MPSoCs and UltraScale+ FPGAs (XAPP1335) describes how to implement security or safety critical designs using the AMD Isolation Design Flow for Fault-Tolerant Systems with the AMD Isolation Design Flow for Fault-Tolerant Systems Vivado Design Suite.

- Vivado Isolation Verifier User Guide

Starting in Vivado 2018.3, Vivado Isolation Verifier (VIV) is integrated with Vivado Design Suite releases and supports UltraScale+ devices (including Zynq UltraScale+). Vivado Isolation Verifier User Guide (UG1291) describes the usage of the Vivado Isolation Verifier (VIV) to verify Isolation in an FPGA/PL design.

- Isolation Design Example for Zynq UltraScale+ MPSoC

The Isolation Design Example for the Zynq UltraScale+ MPSoC (XAPP1336) describes the creation and implementation of a single chip, general purpose, 2 channel system using the Lower Power Domain (LPD) as one channel and a Triple Modular Redundant MicroBlaze™ in the PL. The Isolation Design Flow + Dynamic Function eXchange Example Application Note (XAPP1361) describes the combined flow of IDF and DFX on Zynq UltraScale+ MPSoC devices.

Verification Tools

IDF Verification tools (IVT and VIV) verify that an FPGA design partitioned into isolated regions meet the stringent standards for fail-safe design. IVT and VIV are used at two stages in the FPGA design cycle. They are used first, early in the flow, to perform a series of design rule checks on floorplans and pin assignments. After the design is complete, they are used again to validate that the required isolation is built into the design.

Isolation Verification Tool (IVT) for ISE Design Suite

IVT is an executable that runs outside of ISE but fully within the ISE environment. IVT runs as a set of Design Rule Checks (DRCs) required to prove the design being operated on is isolated. It outputs a graphical display of the design and a verbose text report.

- The IVT.zip file contains:

- IVT Executable

- Release Notes and Installation Guide

- License Agreement

- Lab

Note that the current version of IVT supports Virtex 5, Spartan 6, and the 7 series family of FPGAs and SoCs.

Vivado Isolation Verifier (VIV) for Vivado Design Suite

Starting in 2018.2, Vivado Isolation Verifier is integrated with the Vivado Design Suite release, which supports 7 Series (including Zynq 7000) and UltraScale+ devices (including Zynq UltraScale+). For more information refer to the Vivado Isolation Verifier User Guide (UG1291).

Resources

Stay Informed

Join the adaptive SoC and FPGA notification list to receive the latest news and updates.