Documentation

Explore all Spartan UltraScale+ white papers, data sheets, solution brief, documentation and more.

High I/O, Low-Power FPGAs with State-of-the-Art Security Features

With typical lifespans extending well past 15 years, you can depend on AMD devices for the life of your design—extending AMD 7 Series FPGAs and adaptive SoCs through 2040 and AMD UltraScale+™ FPGAs and adaptive SoCs through 2045.

With more devices and sensors connected at the edge, there's a need for secure devices that can handle large amounts of data. The new cost-optimized high I/O AMD Spartan™ UltraScale+™ FPGA family helps designers rapidly move through these challenges by delivering low cost, power efficiency, and modern security features.

Support Cost-Sensitive Designs Without Difficult Trade-offs

Spartan UltraScale+ FPGAs have it all—delivering a competitive balance of price, power, features, and size to support board management control, I/O expansion, IoT, networking use cases, and more.

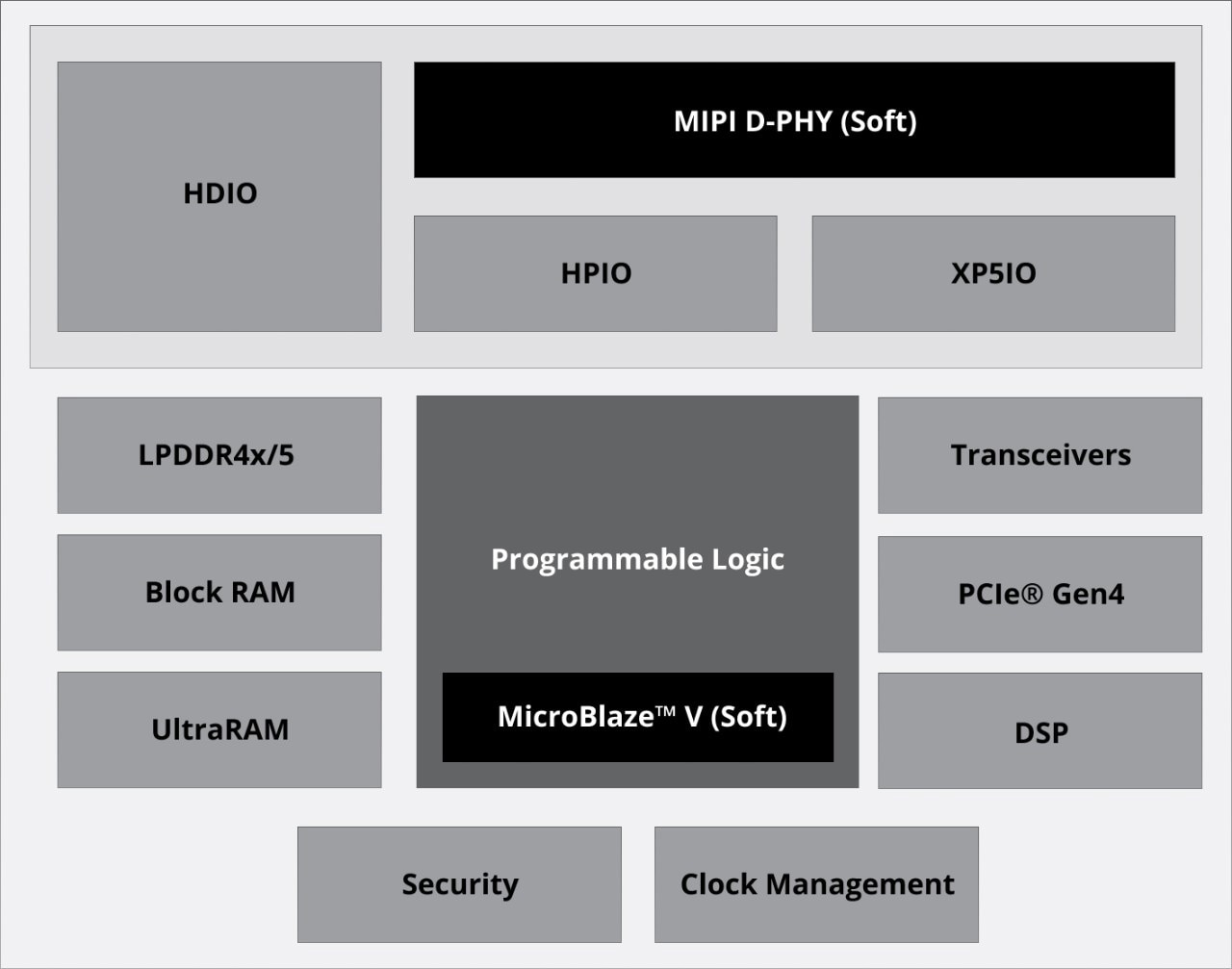

The Spartan UltraScale+ FPGA presents advanced I/O capabilities, low-power consumption, and state-of-the-art security features. Equipped with high-speed transceivers, substantial built-in and external memory, and PCIe® Gen4, this family provides robust solutions for a broad array of applications.

Meet the Performance Requirements of I/O-Intensive Applications

High I/O, low-power, robust security features, and advanced connectivity, all in a small package—learn five reasons to choose Spartan UltraScale+ FPGAs for your designs.

Innovations like machine vision and AI at the edge require new architectures that are flexible, energy efficient, and low cost. This ebook explores the differences between FPGAs, adaptive SoCs, ASICs, and other standard processors to help you decide which approach is best for your application. Learn how you can elevate your next design to meet the increasing complexity of today’s innovations without compromising on performance or efficiency.

Spartan UltraScale+ FPGAs offer high GPIO counts, supporting both legacy and emerging protocols, and 16.3 Gb/s transceivers for networking, video, and vision applications. The devices are also in compliance with industry standards, such as PCIe® Gen4, 10 GE Vision, CoaXPress 2.1, and 12G-SDI, to help accelerate time to market.

Spartan UltraScale+ FPGAs leverage a 16 nm architecture and offer up to a 30% reduction in total power compared to the previous 28 nm devices on lower densities.3 The larger density devices, which include hardened DDR and PCIe interfacing IP, offer an improved power efficiency of up to 60% compared to the previous 28 nm devices4, thereby enhancing overall system performance.

Spartan UltraScale+ FPGAs provide robust, multi-tiered security with NIST-approved post-quantum cryptography, unique device-identification via the physical unclonable function, permanent tamper penalty for device protection, side-attack protection via DPA countermeasures, and adaptable AES-GCM decryption to meet evolving threats.

Complementing the energy efficiency, performance is enhanced by hard IPs, such as the hardened LPDDR4x/5 memory controller, available in select devices. This hardened memory controller allows direct and high throughput access to up to 4.2 Gb/s of memory and reduces FPGA fabric resource utilization for high-value design blocks.

Featuring cost-optimized FPGAs that offer up to 3.2 Gb/s of MIPI performance, the Spartan UltraScale+ family supports advanced camera sensor capture and display. Complete MIPI IP and reference design solutions are also available here. The family’s LVDS performance also enables a range of other protocols, including SLVS-EC (for CMOS image sensors).

The production-proven UltraScale™ architecture, built on TSMC’s 16 nm low-power FinFET process, allows scalability to other 16 nm families as well as the broader portfolio. Developers can leverage the same IP, tool flow, and ecosystem to preserve design investment, enabling a reusable platform across a multi-product portfolio.

Spartan UltraScale+ FPGAs provide low-latency interfacing and processing for various sensors and connectivity standards of machine vision systems in industrial and medical fields. The FPGA family also offers compatibility with a wide range of communication protocols and are available in both compact and low-power devices.

As the demand for advanced data acquisition continues to grow in the market, the Spartan UltraScale+ FPGA offers flexible I/Os, on-chip memory, and efficient processing at the edge. Its low-power consumption, scalable networking, and advanced security features make it ideal for applications like sensor aggregation and point-of-care medical systems.

As server manufacturers’ motherboard designs are becoming more complex, the Spartan UltraScale+ FPGA can provide power management, flexible I/O, and reference designs, such as a general board-management controller, to address the data center server I/O market. The Spartan UltraScale+ FPGA is positioned as a family of devices that can scale with various server host processor motherboards and board management controller cards.

Harnessing the power of advanced broadcast technology, the Spartan UltraScale+ FPGA offers transformative capabilities. With PCIe® Gen4 and hard memory controllers LPDDR4x/5, these cards successfully ingest and transfer high-quality baseband video. Real-time transfer and high-efficiency processing simplify the video capture process and streamline the broadcasting workflow.

| SU10P | SU25P | SU35P | SU50P | SU55P | SU65P | SU100P | SU150P | SU200P | |

|---|---|---|---|---|---|---|---|---|---|

| System Logic Cells (K) | 11 | 22 | 36 | 52 | 52 | 65 | 100 | 137 | 218 |

| DSP Slices | 24 | 36 | 48 | 96 | 96 | 144 | 144 | 384 | 384 |

| Total RAM (Mb)* | 1.77 | 1.84 | 1.93 | 2.91 | 2.91 | 4.31 | 5.89 | 11.65 | 26.79 |

| Transceivers (16.375 Gb/s or 12.5 Gb/s) | 0 | 0 | 0 | 0 | 0 | 4 | 4 | 8 | 8 |

| PCI Express® | 0 | 0 | 0 | 0 | 0 | 1x Gen4x4 | 1x Gen4x4 | 1x Gen4x8 or 2x Gen4x4 | 1x Gen4x8 or 2x Gen4x4 |

| Maximum I/O Pins | 304 | 304 | 304 | 388 | 352 | 478 | 478 | 572 | 572 |

* Total RAM = Maximum Distributed RAM + Total Block RAM + Total UltraRAM

Spartan UltraScale+ FPGA silicon samples will be available in H1’2025. If you are interested in getting early access to the Spartan UltraScale+ family in the Vivado design suite and sample silicon, please contact your AMD sales representative.

The cost-optimized, high I/O Spartan UltraScale+ family built for secure, low-power applications

Our sales team is here to support you in making the best technology decisions based on your specific needs.