Tried. Trusted. Long Lasting.

With typical lifespans extending well past 15 years, you can depend on AMD devices for the life of your design—extending AMD 7 Series FPGAs and adaptive SoCs through 2040 and AMD UltraScale+™ FPGAs and adaptive SoCs through 2045.

AMD Spartan™ UltraScale+™ 产品优势

随着越来越多的器件和传感器连接到边缘设备,市场对能够处理大量数据的安全器件的需求不断增加。AMD 全新推出的成本优化型 Spartan™ UltraScale+™ FPGA 凭借高 I/O、低成本、高能效和现代安全功能,可助力设计师快速应对这些挑战。

高 I/O、低功耗及先进的安全功能

- 采用 28nm 及以下制程工艺的卓越 FPGA,提供出色的 I/O 逻辑单元比1

- 与上一代相比,采用 16nm FinFET 制程工艺的器件总功耗降低了 30%2

使用经验证的设计工具加快设计收敛

- 自 2012 年推出的强大、高品质 Vivado™ Design Suite

- 涵盖从仿真到验证的各个环节,适用于各种类型的 FPGA

依托可信赖的供应商,确保设计一次性成功

- 深耕 FPGA 业务近 40 年,器件出货量达数十亿

- 超过 15 年的产品生命周期和现场可升级性,带来超长设计寿命

加快上市速度

助力成本敏感型设计,无需艰难取舍权衡

Spartan UltraScale+ FPGA 不仅极具性价比,还在功耗、功能与尺寸之间实现了良好平衡,能够很好地支持板卡管理控制、I/O 扩展、物联网以及网络应用等。

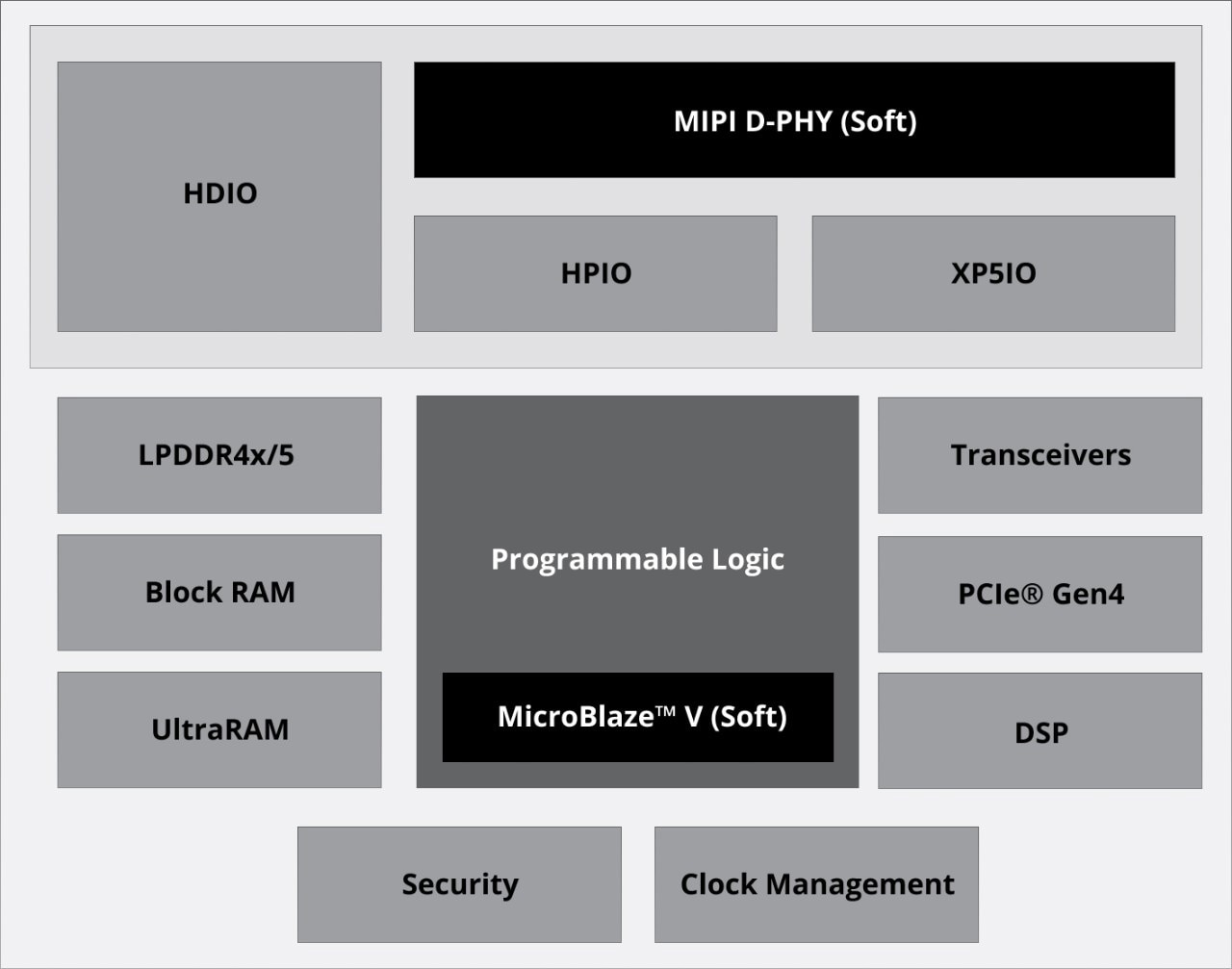

基本构建块

Spartan UltraScale+ FPGA 具有出色的 I/O 功能、低功耗以及先进的安全功能。该系列配备高速收发器、大量内置和外部存储器以及 PCIe® Gen4,为各种应用场景带来强大稳定的解决方案。

为嵌入式系统提供支持

满足 I/O 密集型应用的性能要求

高 I/O、低功耗、强大安全功能及高级连接功能,所有这些都整合在一个小型封装中。了解选择 Spartan UltraScale+ FPGA 助力设计工作的五大理由。

利用成本优化型 FPGA 和自适应 SoC 释放创新潜能

边缘机器视觉及人工智能等创新需要灵活、高能效以及低成本的新架构。本电子书介绍了 FPGA、自适应 SoC、ASIC 以及其他标准处理器之间的差异,可帮助您确定符合自身应用需求的方案。了解如何在不影响性能或效率的情况下,提升您的新一代设计,以充分满足当前日益复杂的创新需求。

特性与优势

- 灵活的 I/O 接口

- 低功耗

- 先进的安全功能

- 硬核存储器控制器

- MIPI 和 LVDS 性能

- 可扩展性

灵活的 I/O 接口

Spartan UltraScale+ FPGA 带来超多通用 I/O (GPIO),支持传统及新兴协议,并配备适用于网络、视频和视觉应用的 16.3Gb/s 收发器。此外,该系列器件还符合 PCIe® Gen4、10GE Vision、CoaXPress 2.1 和 12G-SDI 等行业标准,有助于加快产品上市进程。

低功耗

Spartan UltraScale+ FPGA 采用 16nm 架构,与之前较低密度的 28nm 器件相比,总功耗锐降 30%。3 这款高密度器件配备硬核 DDR 和 PCIe 接口 IP 等,与之前的 28nm 器件相比,能效提升高达 60%4,从而全面提高整体系统性能。

先进的安全功能

Spartan UltraScale+ FPGA 具有稳健的多层安全机制,其中包括经 NIST 批准的后量子加密、通过物理不可克隆功能实现的唯一设备标识、用于设备保护的永久性篡改惩罚、通过 DPA 反制机制实现的旁路攻击保护,以及高适应性 AES-GCM 解密以应对不断发展的安全威胁。

硬核存储器控制器

在提高能效的同时,性能也通过硬 IP(例如特定器件中提供的硬核存储器控制器 LPDDR4x/5)得到增强。这种硬核存储器控制器不仅支持高达 4.2Gb/s 的直接、高吞吐量内存访问,而且还可降低高价值设计模块的 FPGA 架构资源使用率。

MIPI 和 LVDS 性能

Spartan UltraScale+ 系列成本优化型 FPGA 具有高达 3.2Gb/s 的 MIPI 性能,可为高级摄像头传感器的数据捕获与显示提供支持。完整的 MIPI IP 和参考设计解决方案可在此处深入了解。该系列 FPGA 还具有出色的 LVDS 性能,可支持包括 SLVS-EC(面向 CMOS 图像传感器)在内的众多协议。

可扩展性

经过量产验证的 UltraScale™ 架构采用台积电的 16nm 低功耗 FinFET 制程工艺,可扩展至其它 16nm 系列以及更广泛的产品系列。开发者可利用相同的 IP、工具流程和生态系统来保护设计投资,从而为各种产品系列提供可重复使用的平台。

应用

面向机器视觉的灵活 I/O

Spartan UltraScale+ FPGA 可提供低延迟连接和处理能力,符合工业和医疗领域各类传感器及机器视觉系统的连接标准。此外,该 FPGA 系列还与多种通信协议兼容,并提供紧凑型和低功耗产品。

多功能数据采集助力工业和医疗行业发展

Spartan UltraScale+ FPGA 提供高度灵活的 I/O、片上存储器以及高效的边缘处理能力,可充分满足市场对高级数据采集不断增长的需求。该系列 FPGA 具有低功耗、可扩展网络和高级安全功能,非常适合传感器聚合和护理点医疗系统等应用。

面向数据中心的低成本 I/O 扩展与主板管理控制器 (BMC)

在服务器制造商的主板设计变得日益复杂之际,Spartan UltraScale+ FPGA 可提供高效功耗管理、灵活 I/O 和参考设计(例如通用主板管理控制器),可充分满足数据中心服务器 I/O 市场的需求。Spartan UltraScale+ FPGA 系列器件可与各类服务器主机处理器主板和主板管理控制器卡实现同步扩展。

提升视频采集卡的广播效率

凭借强大的高级广播技术,Spartan UltraScale+ FPGA 带来非凡功能。通过 PCIe® Gen4 和硬核存储器控制器 LPDDR4x/5,视频采集卡可成功采集并传输高质量的基带视频。实时传输加上高效处理,不仅可简化视频采集过程,而且还能优化广播工作流程。

产品表

| SU10P | SU25P | SU35P | SU50P | SU55P | SU65P | SU100P | SU150P | SU200P | |

|---|---|---|---|---|---|---|---|---|---|

| 系统逻辑单元 (K) | 11 | 22 | 36 | 52 | 52 | 65 | 100 | 137 | 218 |

| DSP slice | 24 | 36 | 48 | 96 | 96 | 144 | 144 | 384 | 384 |

| 总 RAM (Mb)* | 1.77 | 1.84 | 1.93 | 2.91 | 2.91 | 4.31 | 5.89 | 11.65 | 26.79 |

| 收发器(16.375Gb/s 或 12.5Gb/s) | 0 | 0 | 0 | 0 | 0 | 4 | 4 | 8 | 8 |

| PCI Express® | 0 | 0 | 0 | 0 | 0 | 1x Gen4x4 | 1x Gen4x4 | 1x Gen4x8 或 2x Gen4x4 | 1x Gen4x8 或 2x Gen4x4 |

| 最大 I/O 引脚数 | 304 | 304 | 304 | 388 | 352 | 478 | 478 | 572 | 572 |

* 总 RAM = 最大分布式 RAM + 块 RAM 总计 + UltraRAM

立即体验

抢先体验计划

Spartan UltraScale+ FPGA 芯片样片将于 2025 年上半年提供。如果您有兴趣通过 Vivado Design Suite 和芯片样片抢先体验 Spartan UltraScale+ 系列,请联系您的 AMD 销售代表。

Spartan UltraScale+ FPGA 产品简介

Spartan UltraScale+ 系列具有成本优化和高 I/O 特性,专为安全的低功耗应用打造

支持和资源

联系销售人员

我们的销售团队将会根据您的具体需求帮助您做出最适合的技术决策。

附注

- 依据截至 2024 年 2 月的 Spartan UltraScale+ FPGA 数据表,评估对 28nm 及更低制程 FPGA 的总 I/O 逻辑单元比。(SUS-11)

- 预测数据基于 AMD 实验室 2024 年 1 月的内部分析,根据 Artix™ UltraScale+ AU7P FPGA 的逻辑单元数量差异计算总功耗(静态及动态功耗),以使用 Xilinx Power Estimator (XPE) 工具(版本 2023.1.2)估算 16nm Spartan UltraScale+ SU35P FPGA 与 28nm Artix 7 7A35T FPGA 的功耗。实际总功耗在最终产品上市时可能会有所不同,具体取决于配置、设计、使用情况和其他因素。(SUS-03)

- 预测数据基于 AMD 实验室 2024 年 1 月的内部分析,根据 Artix™ UltraScale+ AU7P FPGA 的逻辑单元数量差异计算总功耗(静态及动态功耗),以使用 Xilinx Power Estimator (XPE) 工具(版本 2023.1.2)估算 16nm Spartan UltraScale+ SU35P FPGA 与 28nm Artix 7 7A35T FPGA 的功耗。实际总功耗在最终产品上市时可能会有所不同,具体取决于配置、设计、使用情况和其他因素。(SUS-03)

- 预测数据基于 AMD 实验室 2024 年 1 月的内部分析,根据 Artix UltraScale+ AU7P FPGA 的逻辑扩展数量计算总功耗(静态及动态功耗),以使用 Xilinx Power Estimator (XPE) 工具(版本 2023.1.2)估算 Spartan UltraScale+ SU200P FPGA 与 Artix 7 7A200T FPGA 的总功耗。实际总功耗在最终产品上市时可能会有所不同,具体取决于配置、使用情况和其他因素。(SUS-06)

- 依据截至 2024 年 2 月的 Spartan UltraScale+ FPGA 数据表,评估对 28nm 及更低制程 FPGA 的总 I/O 逻辑单元比。(SUS-11)

- 预测数据基于 AMD 实验室 2024 年 1 月的内部分析,根据 Artix™ UltraScale+ AU7P FPGA 的逻辑单元数量差异计算总功耗(静态及动态功耗),以使用 Xilinx Power Estimator (XPE) 工具(版本 2023.1.2)估算 16nm Spartan UltraScale+ SU35P FPGA 与 28nm Artix 7 7A35T FPGA 的功耗。实际总功耗在最终产品上市时可能会有所不同,具体取决于配置、设计、使用情况和其他因素。(SUS-03)

- 预测数据基于 AMD 实验室 2024 年 1 月的内部分析,根据 Artix™ UltraScale+ AU7P FPGA 的逻辑单元数量差异计算总功耗(静态及动态功耗),以使用 Xilinx Power Estimator (XPE) 工具(版本 2023.1.2)估算 16nm Spartan UltraScale+ SU35P FPGA 与 28nm Artix 7 7A35T FPGA 的功耗。实际总功耗在最终产品上市时可能会有所不同,具体取决于配置、设计、使用情况和其他因素。(SUS-03)

- 预测数据基于 AMD 实验室 2024 年 1 月的内部分析,根据 Artix UltraScale+ AU7P FPGA 的逻辑扩展数量计算总功耗(静态及动态功耗),以使用 Xilinx Power Estimator (XPE) 工具(版本 2023.1.2)估算 Spartan UltraScale+ SU200P FPGA 与 Artix 7 7A200T FPGA 的总功耗。实际总功耗在最终产品上市时可能会有所不同,具体取决于配置、使用情况和其他因素。(SUS-06)