ChipScope 功能与特性

许多硬件问题只有在整个集成系统实时运行的过程中才会显现出来。Vivado ChipScope 提供了一套完整的调试流程,可在系统运行期间最大限度提升对可编程逻辑的观测能力,助力设计调试。

设计观测

可观测的内部节点数量增至数百个,设计的内部工作情况一目了然。

深入分析

实施复杂的触发条件并对设计进行多角度的深入分析。

快速调试迭代

利用增量编译流程加快迭代,并使用 Python™ 实现任务自动化。

硬件调试分步操作教程(作者:Adam Taylor)

Adam Taylor 针对 AMD Versal™ 和 UltraScale+™ 器件各编制了一套教程,通过这两套教程,可了解如何使用 Vivado ChipScope 在真实的系统中进行硬件调试。每套演示教程都着重介绍了调试方法,并展示了如何有效地检测设计,还包括多项可运行和探索的项目。

全面的调试流程

采用灵活的方法进行调试 IP 检测、设计分析和运行时配置,并通过增量编译加快调试迭代。

调试 IP

对于互连结构调试流程而言,通过一组 IP 核在不妨碍设计功能的情况下实现设计可见性至关重要。所有 AMD 调试 IP 均可在线获取,也可通过 Vivado Design Suite 中的 IP 目录获取。请注意,针对 Versal™ 自适应 SoC 的可编程逻辑调试必须基于 AXI。

FPGA 和 Zynq™ 自适应 SoC |

AMD Versal 自适应 SoC |

|

Integrated Logic Analyzer (ILA) |

||

System ILA |

||

Virtual Input/Output (VIO) |

||

BSCAN-to-JTAG Converter |

- |

|

Debug Hub* |

System Debug Bus (XSDB) – 内置 |

*Debug Hub 支持通过 JTAG 与调试 IP 核进行通信

数据线缆模块

AMD 针对异构系统的标准 JTAG 调试和高速调试提供了一系列数据线缆。无论您的首要任务是捕获大量数据,还是充分降低设备资源利用率,亦或是提升调试性能,选择正确的数据线缆至关重要,因为这会影响工作流程效率。

除了数据线缆模块之外,大多数评估套件还提供内置的 USB 转 JTAG 调试接口,而且部分器件系列支持通过以太网或 PCI-Express® 进行调试。在下面了解有关数据线缆模块的更多信息。

| 器件支持 | 平台线缆 USB II | SmartLynq | SmartLynq+ |

|---|---|---|---|

| AMD FPGA | ✓ | ✓ | |

| Zynq 自适应 SoC | ✓ | ✓ | |

| Versal 自适应 SoC | ✓ | ✓ |

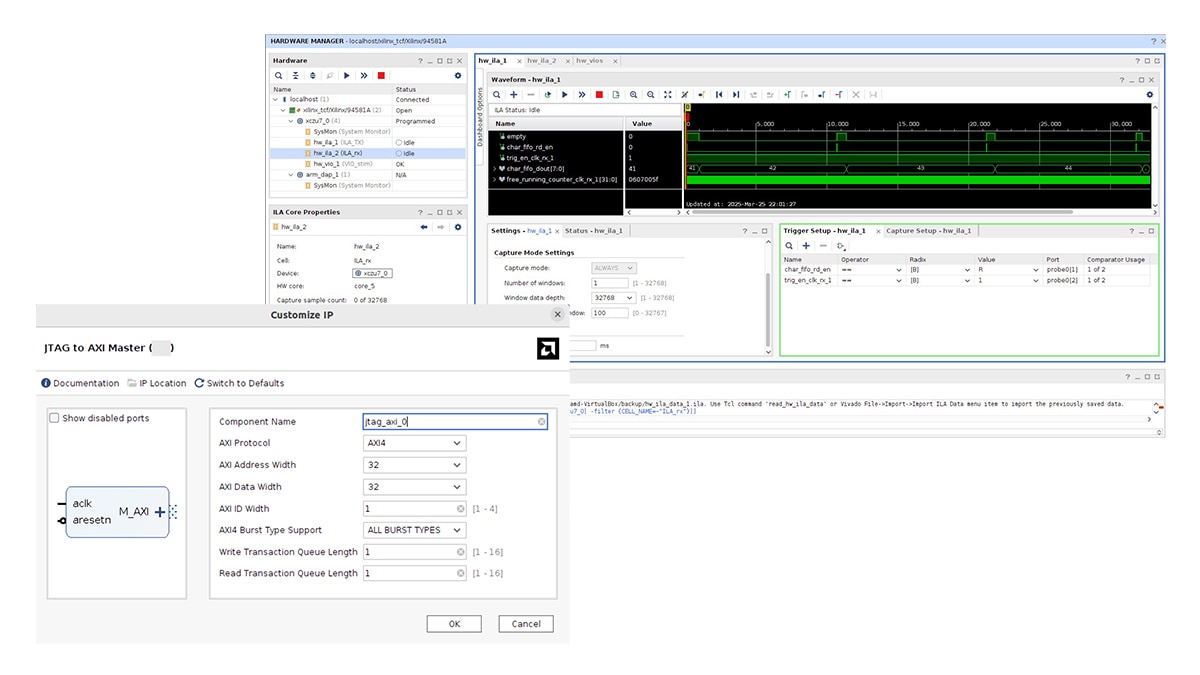

设计分析

ChipScope 针对系统内调试和跟踪提供了多种接口和自动化方法。在 Vivado IDE 中,设计人员可以在高层次波形和设计元素之间无缝切换,并通过 TCL 或 Python 自动执行交互。

- 复杂触发器:设置具有基于状态的依赖关系的多级触发器,以重现复杂的设计情形。

- 交叉探测:能够执行从调试输出到 RTL 或网表的交叉探测,从而据此分析和确定设计错误的根源。

- 波形分析:显示捕获的信号转换以及触发器信息注解,以便能够追溯到设计源文件。

- 协议调试:执行特定于协议的分析和事务处理时间分析,以识别瓶颈,并从协议事件到 RTL 进行交叉探测。

- VIO 接口:促进释放用于交互式测试和监控的信号,而不导致设计停止或重编程。

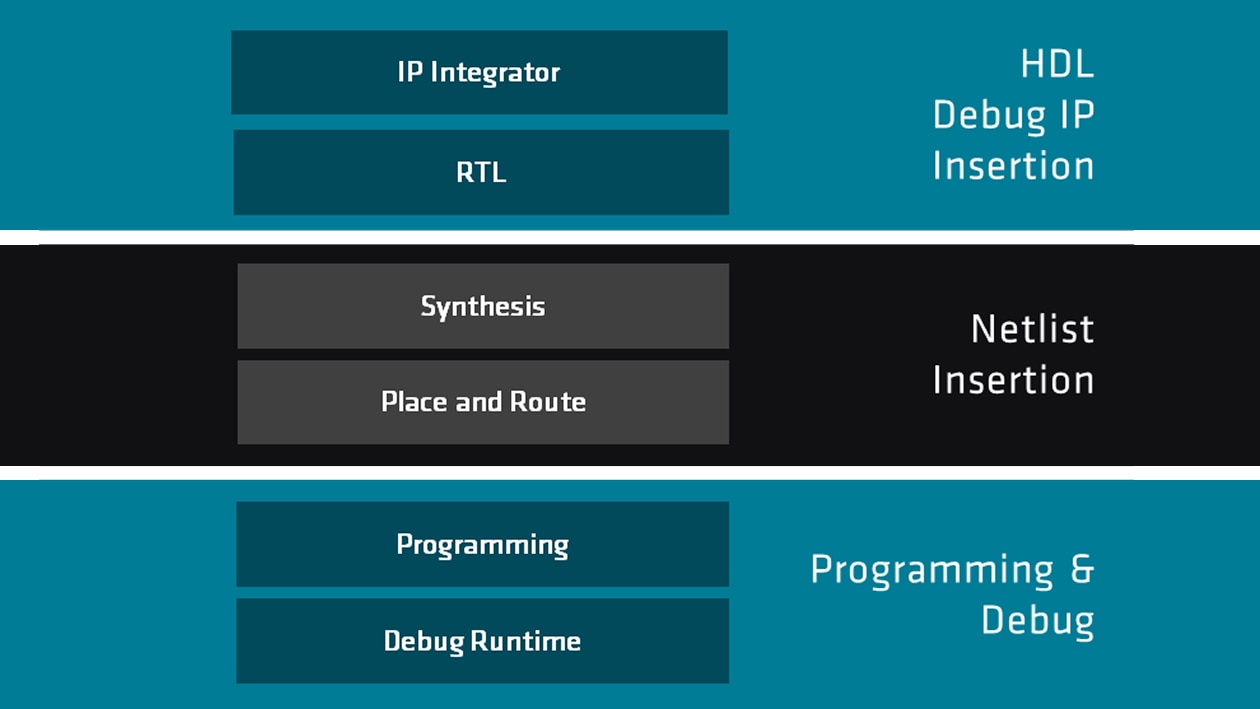

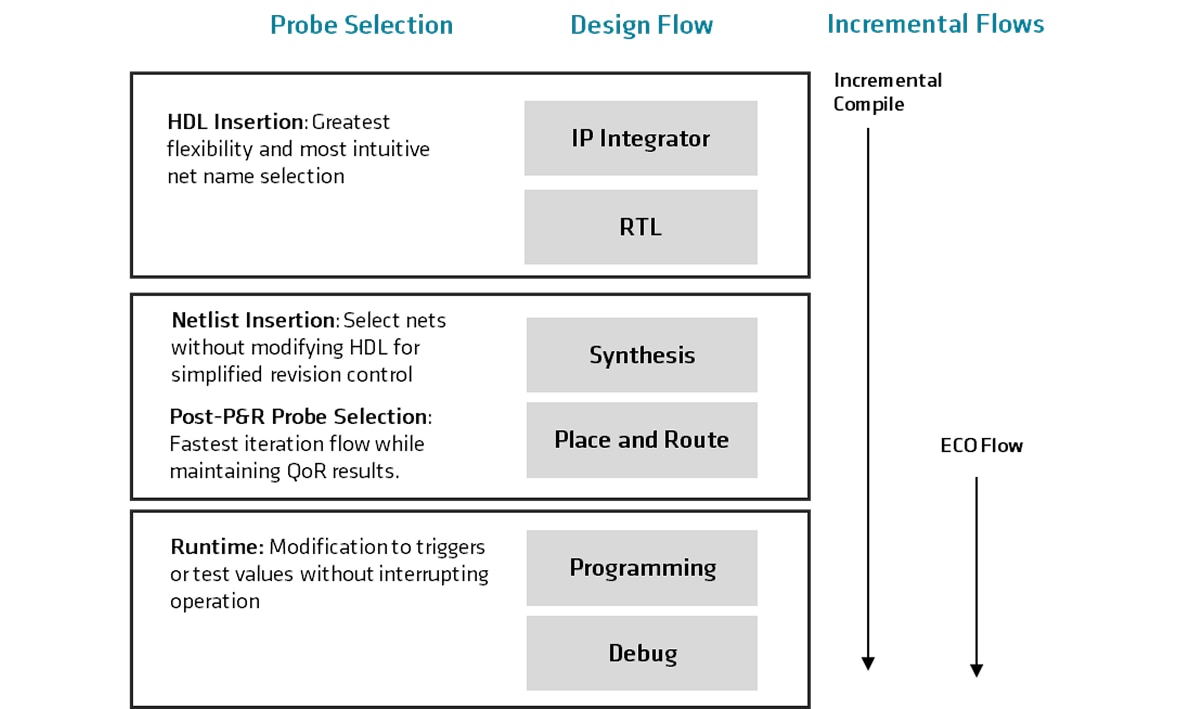

快速调试迭代

增量编译流程

随着漏洞不断显现,修改触发器、探测器和调试核不可避免,因此快速迭代变得至关重要。ChipScope 采用多种增量编译流程,支持仅修改设计中需要更改的部分,从而避免在调试周期完全重建。

多个增量编译流程可供使用,具体取决于调试方法:

- 增量编译:对设计中需要更改的部分执行综合和布局布线

- ECO 流程:完成布局布线后选择探测器 – 非常适合进行细微更改,可充分加快迭代速度并最大程度地保存设计

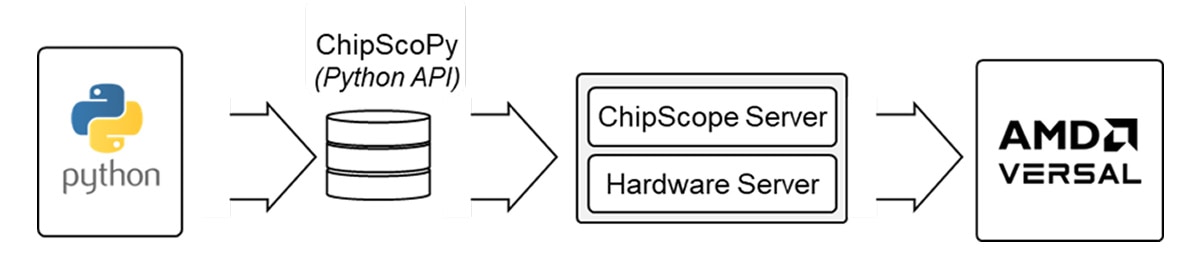

ChipScoPy:利用 Python API 实现自动化

对于 Versal 器件,ChipScoPy 是一个简单的 Python 接口,可在无需使用 Vivado IDE 的情况下自动执行 ChipScope 功能,从而更好地自动执行和控制可编程逻辑和各类硬核 IP 的调试过程。

各种优势包括:

- 流程灵活多变,支持用户自定义,而且可完全通过脚本控制

- 流程高度可扩展,可使用第三方和开源软件包(如 Plot Viewer)

- 无需安装 Vivado 工具,因此安装占用空间更小