-

Vivado IP Integrator Key Features and Benefits

- Tight Integration within the Vivado Integrated Design Environment

- Seamless inclusion of IP Integrator hierarchical subsystems into the overall design

- Rapid capture and packaging of IP Integrator designs for reuse

- Support for both graphical and Tcl-based design flows

- Rapid simulation and cross-probing between multiple design views

- Support for All Design Domains

- Support for processor or processor-less designs

- Integration of algorithmic (Vitis HLS and Model Composer) and RTL-level IP

- Combination of DSP, video, analog, embedded, connectivity, and logic

- Support for Project based DFX Flow

- Focus on Designer Productivity

- DRCs on complex interface level connections during design assembly

- Recognition and correction of common design errors

- Automatic IP parameter propagation to interconnected IP

- System-level optimizations

- Automated designer assistance

- Enhanced Collaboration Support

- Enhanced Collaboration Support

- Team Based designs using Block Design Container enables reusability and modular designs

- Revision control improvements separating source files from generated files

- Block Design Diff tool to compare two Block Designs

High-Level Design Features

Here's a quick overview of Vivado™ Design Suite features for Accelerating High-Level Design. Click the other tabs for complete feature details..

- Vitis HLS

- IP Integrator

- Abstract Shell

- Vitis Model Composer

Vitis High-Level Synthesis Tool

The advanced algorithms used today in AI, wireless, medical, defense, and consumer applications are more sophisticated than ever before. The Vitis™ High-Level Synthesis tool, included as a no-cost upgrade in all Vivado™ Editions, accelerates IP creation by enabling C++ specifications to be directly targeted into AMD programmable devices without the need for manually creating equivalent RTL designs. The Vitis HLS tool supports both the Vitis and Vivado design environments, and enables software and hardware designers alike to accelerate kernel or IP creation through:

- Abstraction of algorithmic descriptions, data type specifications with fixed-point or floating-point integers, and interfaces (FIFO, memories, AXI4)

- Extensive libraries for including built-in support for arbitrary precision data types, streams, and vectorized data types

- Directive-driven, architecture-aware synthesis with high QoR

- Fast time to QoR that rivals hand-coded RTL

- Accelerated verification using C/C++ test bench simulation and automatic VHDL or Verilog simulation and test bench generation

- Automatic use of AMD on-chip memories and DSP elements, including for floating-point types

Libraries

The following built-in libraries are included with the Vitis HLS tool:

| Name | Description |

|---|---|

Arbitrary Precision Data Types |

Integer and fixed-point (ap_int.h) types |

HLS Streams |

Models for streaming data structures—designed to obtain best performance and area (hls_stream.h) |

Vector types |

Vectorized types and operations (hls_vector.h) including for arbitrary precision types |

HLS Math |

Extensive support for the synthesis of standard C (math.h) and C++ (cmath.h) math libraries. Support includes floating-point and fixed-point functions: abs, atan, atanf, atan2, atan2, ceil, ceilf, copysign, copysignf, cos, cosf, coshf, expf, fabs, fabsf, floorf, fmax, fmin, logf, fpclassify, isfinite, isinf, isnan, isnormal, log, log10, modf, modff, recip, recipf, round, rsqrt, rsqrtf, 1/sqrt, signbit, sin, sincos, sincosf, sinf, sinhf, sqrt, tan, tanf, trunc |

The Vitis HLS tool also supports the Vitis performance-optimized libraries available on GitHub with out-of-the-box acceleration and minimal-to-zero code changes to your existing applications. These common Vitis accelerated-libraries include advanced math, statistics, linear algebra, and DSP to offer core functionalities for a wide range of applications. These libraries offer acceleration for workloads such as vision and image processing with OpenCV functions, quantitative finance, database, data analytics, data compression, and more.

For more information, please visit the Vitis HLS site.

IP Integrator

The Vivado™ Design Suite shatters the RTL design productivity plateau by providing the industry’s first plug-and-play IP integration design environment, with its IP Integrator feature.

Vivado IP Integrator provides a graphical and Tcl-based, correct-by-construction design development flow. It provides a device and platform aware, interactive environment that supports intelligent auto-connection of key IP interfaces, one-click IP subsystem generation, real-time DRCs, and interface change propagation, combined with a powerful debug capability.

Designers work at the “interface” and not “signal” level of abstraction when making connections between IP, greatly increasing productivity. Often times this is using industry standard AXI4 interfaces, but dozens of other interfaces are also supported by IP integrator.

Working at the interface level, design teams can rapidly assemble complex systems that leverages IP created with Vitis HLS, Model Composer, AMD SmartCore™ and LogiCORE™ IP, Alliance Member IP as well as your own IP. By leveraging the combination of Vivado IPI and HLS customers are saving up to 15X in development costs versus an RTL approach.

C-based IP Generation with Vitis High-Level Synthesis & Vitis Model Composer

As the leading provider of Electronic System Level Design tools for programmable solutions, Vivado provides Vitis™ High-Level Synthesis for C, C++ and SystemC, and you can buy an add-on Vitis model composer for DSP. These solutions enable high-level IP specifications to be directly synthesized into VHDL and Verilog, accelerating IP verification over 100X and RTL creation by up to 4X. The highly integrated tools can be used individually or in combination with the result being reusable IP for use in the Vivado ML Suite.

Fast Compile using Abstract Shell

Abstract Shell is a new technology that enables fast compile for complex and large designs. It allows users to define reconfigurable modules within a design to be compiled independently. Users can select portions of the design to be modified and recompiled without having to recompile the entire design.

Abstract Shell enables an average compile time reduction of 5x and up to 17x compared to a traditional compilation. This features also allows users to define multiple modules within the design that can be compiled in parallel.

Key Features

Abstract Shell enables users to:

- Reduce runtime and memory usage for each reconfigurable module compilation

- Implement all reconfigurable modules in parallel for multiple reconfigurable partitions

- Hide any proprietary information that exists within the static design

- Avoid license checking for any IP that exists in the static design

- Distribute reconfigurable partitions among multiple teams for team-based design collaboration

Testimonials

Vitis Model Composer

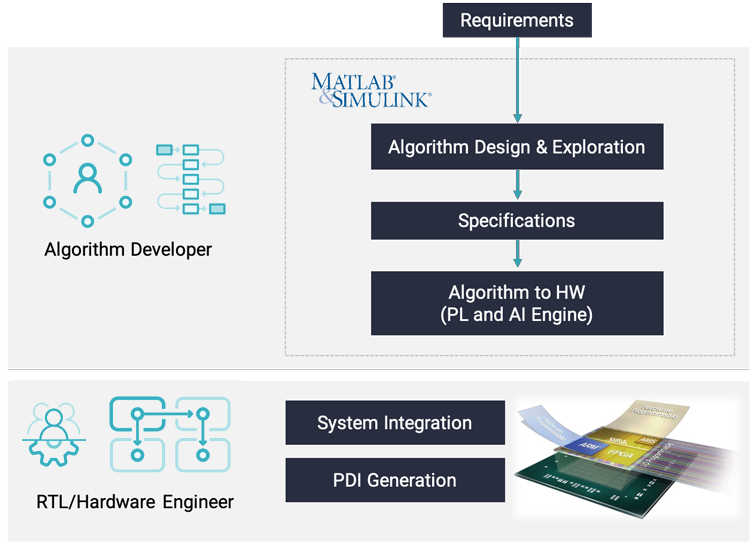

Vitis™ Model Composer is a Model-Based Design tool that enables rapid design exploration within the MathWorks MATLAB® and Simulink® environment and accelerates the path to production on AMD devices through automatic code generation. You can design your algorithms and iterate through them using high-level performance-optimized blocks and validate functional correctness through system-level simulations. Vitis Model Composer transforms your design to production-quality implementation through automatic optimizations. The tool provides a library of more than 200 HDL, HLS, and AI Engine blocks for the design and implementation of algorithms on AMD devices. It also enables importing custom HDL, HLS, and AI Engine code as blocks into the tool. Vitis Model Composer includes all the functionality of AMD System Generator for DSP which is no longer shipped as a standalone tool since 2020.2.

In Vitis Model Composer you can:

- Create a design using optimized blocks targeting AI Engines and Programmable Logic.

- Visualize and analyze simulation results and compare the output to golden references generated using MALTAB® and Simulink®.

- Seamlessly co-simulate AI Engine and Programmable Logic (HLS, HDL) blocks.

- Automatically generate code (AI Engines dataflow graph, RTL, HLS C++) and testbench for a design.

- Import custom HLS, AI Engines, and RTL code as blocks.

Note:

Vitis Model composer can be purchased as an add-on license to any Vivado Design Suite Edition.

For more information on how to download and buy please visit the Vitis Model Composer page.

Key Features

-

Accelerate Design Iterations

- High-Level of Abstraction:

Algorithm-centric building blocks, with a focus on functionality, provide ease-of-use essential for domain experts to accelerate design exploration.

- Support for Vectors and Matrices:

Enables frame-based algorithm design that saves you the time and effort to move to an intermediate low-level model for implementation.

- Application-Specific Libraries:

Performance-optimized DSP, Computer Vision, Math, and Linear Algebra libraries available as blocks for simulation and high-performance implementation on AMD devices.

- Import synthesizable C/C++ as Custom Blocks:

The ability to create your own custom blocks for simulation and code generation provides greater flexibility to design your differentiated algorithms

- Seamless Integration with Simulink:

Direct connection with blocks from the Simulink product family enables system-level modeling and simulation and the ability to fully leverage the stimulus generation and data visualization capabilities of Simulink's graphical environment.

- Integer, Floating and Fixed-point Support:

Supports the native floating and integer data types in Simulink and the fixed-point and half data types supported by Vitis HLS.

-

Transform Algorithm to Architecture

- Automatic optimizations:

Analyses your algorithmic specification within Simulink and performs automatic optimizations to steer towards a micro-architecture that optimizes for throughput, reduces Block RAM utilization, and enables concurrent execution of blocks.

- Accelerate IP Creation:

Transform your simulated-able designs into an RTL IP package that you can use within the Vivado IP Integrator and leverage all the benefits of its plug-and-play IP Integration design environment for complex designs.

- Extend to System Generator for DSP:

Leverage the benefits of Model Composer's ease-of-use and simulation speed, for portions of your design and export the synthesized RTL into your existing System Generator for DSP designs as new custom blocks.

- Export to Vitis HLS:

Advanced feature that provides a link between Simulink's graphical environment to design, simulate and validate your algorithms and Vitis HLS, by automatically generating everything you would need to further optimize your algorithm, including test vectors logged from simulation.

- User Interface to Map RTL Interfaces:

Easy to use the graphical interface to map the inputs and outputs in your design to supported RTL interfaces (AXI4-Lite, AXI4-Stream, AXI4-Stream Video, FIFO, Block RAM) and video formats (AXI4-Stream Video) for implementation.

Automatic Test Bench Generation: Automatic logging of test vectors from simulation and generation of a test bench to verify functional equivalence between the executable design and generated code.

- Integer, Floating and Fixed-point Support:

Supports the native floating and integer data types in Simulink and the fixed-point and half data types supported by Vitis HLS.