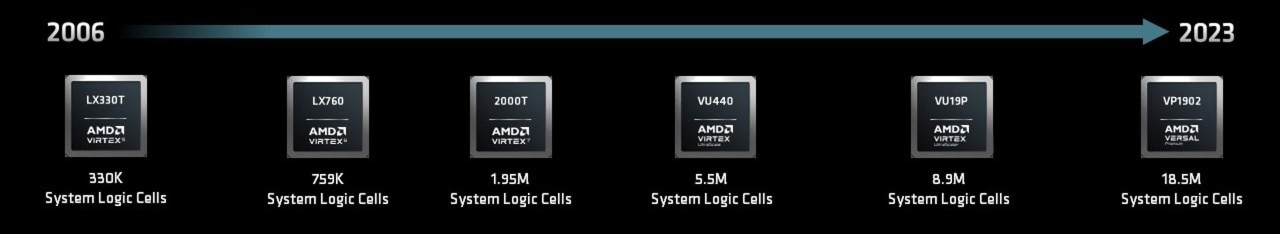

硬件辅助验证领域的先行者

AMD 在硬件辅助验证领域通过创新采用自适应 SoC 和 FPGA 进行仿真与原型设计,为 SoC 系统建模和验证带来革命性突破。AMD 拥有超过 17 年的该领域专业经验,致力打造快速、准确的仿真与原型设计先进解决方案。

6 代领先的硬件辅助验证

超大容量自适应 SoC

- 6 代超大自适应 SoC1

- 与前几代产品相比,可实现容量 2 提高 2 倍、性能 3 提高 2 倍的行业解决方案

先进的设计可见性与调试功能

- 增强了调试硬件功能,可缩短设计验证周期

- 继续投资调试工具和 IP,以实现性能设计可见性

为仿真和原型设计构建的编译工具

- AMD Vivado ML 机器学习增强型报告和迭代设计有助于提高开发人员的工作效率

- AMD Vivado 新一代布局布线功能可扩展至更大的 FPGA 中,显著改进 QoR 和缩短编译时间。

应用

产品系列

成功案例

立即体验

利用 AMD Versal Premium 开展原型设计

AMD Versal Premium VP1902 器件:超大自适应 SoC

- 逻辑密度 2 比 Virtex UltraScale+ VU19P 器件高 2 倍

- 2 倍 I/O 带宽 5 和 2.3 倍收发器带宽 6,助力实现扩展

- 更低 I/O 时延,2*2 SLR 阵列,系统性能更高

附注

- 基于 AMD 在 2023 年 5 月进行的内部分析。(VER-009)

- 基于 AMD 在 2023 年 5 月进行的内部分析,比较 Versal Premium VP1902 器件与 Virtex UltraScale+ VU19P 器件的系统逻辑单元数较。(VER-001)

- 基于 AMD 2023 年 5 月的内部系统时钟性能分析,通过一系列不同尺寸的设计方案对 Versal Premium VP1902 器件和 Virtex UltraScale+ VU19P 器件进行了比较。(VER-006)

- N/A

- 基于 AMD 实验室测试,使用 A6865 封装来仿真 AMD Versal Premium VP1902 器件的 XPIO 数据速率性能,并与 AMD Virtex UltraScale+ VU19P FPGA 的公布数据速率进行了对比。实际结果会有所不同。(VER-003)

- 基于 AMD 实验室在 2023 年 5 月对 Versal Premium VP1902 器件 B6865 封装与 Virtex UltraScale+ VU19P 器件 B3824 封装的总收发器带宽的计算,假设 GTY/GTYP 以 32G 运行、GTM 以 56G 运行。(VER-005)

附注

- 基于 AMD 在 2023 年 5 月进行的内部分析。(VER-009)

- 基于 AMD 在 2023 年 5 月进行的内部分析,比较 Versal Premium VP1902 器件与 Virtex UltraScale+ VU19P 器件的系统逻辑单元数较。(VER-001)

- 基于 AMD 2023 年 5 月的内部系统时钟性能分析,通过一系列不同尺寸的设计方案对 Versal Premium VP1902 器件和 Virtex UltraScale+ VU19P 器件进行了比较。(VER-006)

- N/A

- 基于 AMD 实验室测试,使用 A6865 封装来仿真 AMD Versal Premium VP1902 器件的 XPIO 数据速率性能,并与 AMD Virtex UltraScale+ VU19P FPGA 的公布数据速率进行了对比。实际结果会有所不同。(VER-003)

- 基于 AMD 实验室在 2023 年 5 月对 Versal Premium VP1902 器件 B6865 封装与 Virtex UltraScale+ VU19P 器件 B3824 封装的总收发器带宽的计算,假设 GTY/GTYP 以 32G 运行、GTM 以 56G 运行。(VER-005)