Overview

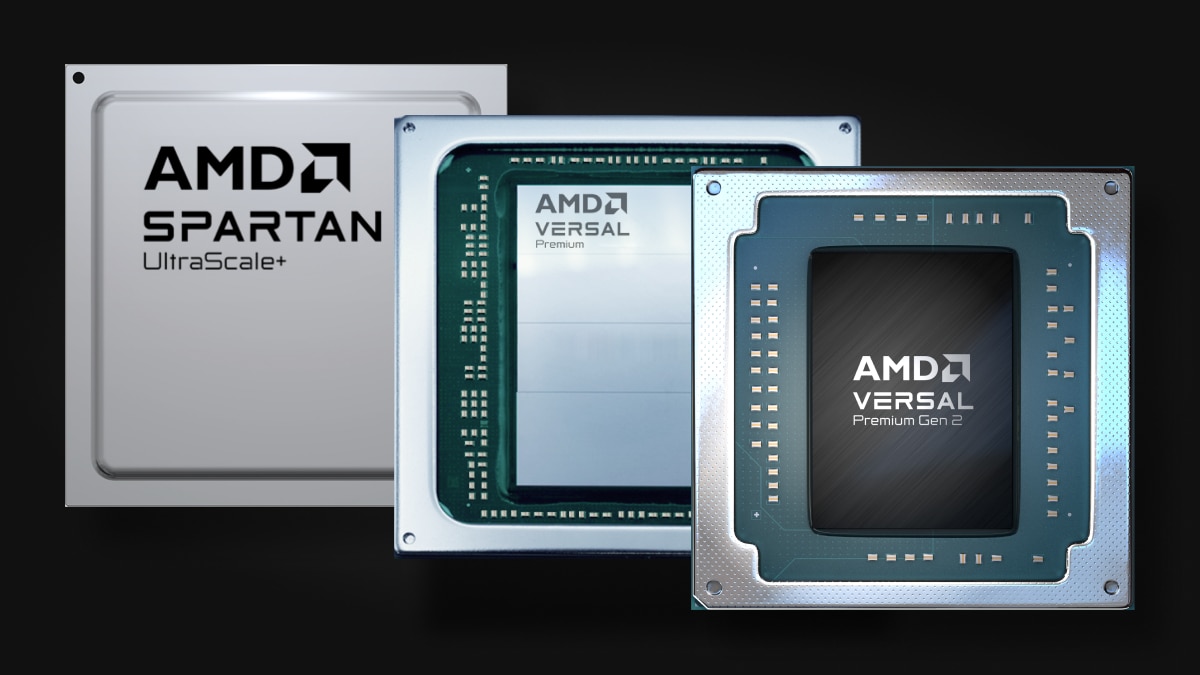

Accelerated by the demands for AI, the need for data processing and faster connectivity increases, making efficiency crucial to minimize the delay from data to insights. The AMD adaptive SoC and FPGA portfolio has a proven track record and will help you meet your product goals through unparalleled system-level efficiencies and supply chain resiliency. Choose AMD and unlock the future of adaptive computing solutions.

Unlock More System-Level Value

The AMD Versal™ adaptive SoC portfolio empowers architects to innovate with cutting-edge technology, foundational hard IP, streamlined software design flow and tools, advanced process nodes, and packaging.

Maximize Supply Chain Confidence

AMD ensures consistent product availability and predictable lead times, minimizing supply chain risk through strategic vendor selection, geographically diverse manufacturing, and assurance programs.

Rely on a Proven Partner

Choosing AMD as your partner ensures you get stability, continuity, and a solid roadmap to help you stay ahead of the competition.

AMD Benefits

The AMD multi-faceted strategy embraces technological innovation, diversifies the supply chain, and enhances supply resiliency and agility.

Unmatched Compute Efficiency

The optimized hard IP in Versal adaptive SoCs results in higher system-level performance-per-watt.1 The AMD Versal RF Series offers 3X more compute per area compared to competing FPGAs.2 In addition, Versal AI Edge Series Gen 2 and Prime Series Gen 2 achieve 10X scalar compute and 3X TOPS/watt compared to previous generation architectures.3,4

To learn about the system-level benefits of the AMD Versal architecture and comparative performance to competing programmable logic based devices, read our white paper: System-Level Benefits of the Versal Platform .

Superior Design with Portfolio-Wide NoC

AMD Versal adaptive SoCs support a fully programmable network on chip (NoC), implemented as hard IP, across the entire portfolio. Hardware designers can benefit from up to a 58% lower write latency, up to a 60% reduction in logic utilization, and up to a 50% reduction in development times versus competing FPGAs.5, 6, 7

Developers who are new to the Versal programmable NoC should check out our Modular NoC training videos.

Optimize Design Efficiency with the Versal Adaptive SoC Programmable NoC

All AMD Versal adaptive SoCs feature a portfolio-wide programmable NoC, replacing traditional AXI interconnects in the programmable logic (PL). With the Versal programmable NoC, you can achieve higher levels of design efficiency and performance than is possible with competing devices.

Better Thermal Resistance

Innovative world-class AMD packaging technology reduces thermal resistance by up to 11X and helps lower power consumption, reducing cost and weight and supporting a wider ambient temperature range.8

Addressing Thermal Challenges with Innovative Packaging Solutions

Deploying mid to high-end FPGAs in demanding environments requires advanced thermal management solutions. Read this white paper to understand AMD advantages versus the competition.

Faster Connectivity

AMD Versal adaptive SoCs provide the fastest LPDDR5 memory connectivity,9 2X faster secure data transactions versus competing FPGAs,10 and enhanced host connectivity. AMD Versal Premium Series Gen 2 is the industry’s first adaptive SoC and FPGA with PCIe® Gen 6 and CXL® 3.1, scaling data transfer rates to 64 Gb/s to support memory- and data-intensive workloads.11

Maximize Supply Chain Confidence

AMD oversees the entire manufacturing supply chain, from raw materials to fabrication, and ensures that all suppliers adhere to high business continuity plan (BCP) standards. AMD delivers consistent product availability, predictable lead times, transparency, and reduced risk.

Together with our supply chain and industry partners, AMD embraces the opportunity to meet demand while driving social and environmental progress in the supply chain. Learn more about our supply chain responsibility.

Boosting Supply Chain Agility and Resiliency in a Dynamic Global Environment

Learn how the AMD holistic approach helps minimize supply risk.

Listicle

White Papers

Applications

Portfolio

Resources

Contact

Get started with AMD adaptive SoCs and FPGAs.

Footnotes

- Based on AMD testing in January 2025, using the AMD Power Design Manager 2024.2 to estimate the total power consumption of a single 18x12 AXI crossbar design with 24 transceivers, synthesized and implemented with Vivado Design Suite 2024.2, on the Versal Prime Series VM1402 device with the programmable NoC, versus the total power consumption of the same single design, synthesized and implemented with Altera Quartus 24.1, on the Altera Agilex 7 AGFB023 device with open-source AXI soft IP and estimated with Altera Quartus Power Thermal Calculator 24.2. Results assume a fixed junction temperature (ΘJC) of 100°C and maximum process leakage devices. Results will vary based on architecture, device, customer design specifications, system configuration, and other factors. (VER-090)

- Based on an AMD internal analysis comparing the theoretical processing capability (including hard IP, AI Engines, and DSP) of the Versal RF Series VR19xx devices versus the largest Altera Agilex 9 Direct RF-Series ARGW027 device. Results may vary based on device, design, configuration, and other factors. (VER-072)

- Based on the projected combined total DMIPs of the Versal AI Edge Series Gen 2 and Versal Prime Series Gen 2 processing systems when configured with 8 Arm Cortex-A78AE applications cores @2.2 GHz & 10 Arm Cortex-R52 real-time cores @1.05 GHz, compared to the published combined total DMIPs of the processing systems in the first generation Versal AI Edge Series and Versal Prime Series. Versal AI Edge Series Gen 2 and Prime Series Gen 2 operating conditions: Highest available speed grade, 0.88V PS operating voltage, split-mode operation, maximum supported operating frequency. First generation Versal AI Edge Series and Prime Series operating conditions: Highest available speed grade, 0.88V PS operating voltage, maximum supported operating frequency. Actual DMIPs performance will vary when final products are released in market. (VER-027)

- TOPS/watt is based on AMD internal performance and power projections for the AIE-ML v2 compute tile architecture in the Versal AI Edge Series Gen 2 using the MX6 data type, compared to performance specifications and AMD Power Design Manager power results for the AIE-ML compute tile architecture featured in the first generation Versal AI Edge Series using the INT8 data type. Operating conditions: 1 GHz FMAX, 0.7V AIE operating voltage, 100°C junction temperature, typical process, 60% vector load, % activations = 0 < 10%. Actual performance will vary when final products are released in market. (VER-023)

- Based on AMD testing in January 2025, measuring the DDR read and write latency of a single multi-manager bridge design, implemented with AMD Vivado Design Suite 2024.1 and the AMD Versal Premium Series VP1202 device using the programmable NoC, versus the same design implemented with Altera Quartus 24.1, on the Altera Agilex 7 AGFB027 device using open-source AXI soft IP. Results will vary based on architecture, device, customer design specifications, system configuration, and other factors. (VER-086)

- Based on AMD testing in January 2025, comparing the post-implementation logic resource utilization of a single 18x12 AXI crossbar design with 24 transceivers, using the AMD Versal Prime Series VM1402 device with the programable NoC, implemented with AMD Vivado 2024.1 versus the Altera Agilex 7 AGFB023 device with open-source AXI soft IP, implemented with Altera Quartus 24.1. Results will vary based on architecture, device, customer design specifications, system configuration, and other factors. (VER-085)

- Based on AMD analysis in January 2025, summing the synthesis and implementation build times of a single 12x12 AXI crossbar design implemented with AMD Vivado 2024.2 on the AMD Versal Prime Series VM1402 device with the programmable NoC, versus the same design implemented with Altera Quartus 24.1, on the Altera Agilex AGFB023 device with open-source AXI soft IP. Results will vary based on architecture, device, customer design specifications, system configuration, and other factors. (VER-088)

- Based on AMD internal analysis in January 2025, using the AMD device and package thermal model to compare the JEDEC two-resistor thermal resistance Junction-to-Case (ΘJC) of the Versal Prime Series VM1802 device in a Versal VFVC1760 lidded package, versus the JEDEC two-resistor thermal resistance Junction-to-Case (ΘJC) of the same device in a Versal VSVD1760 lidless package with a stiffener ring. Results will vary based on architecture, device, customer design specifications, system configuration, and other factors. (VER-087)

- Based on AMD internal analysis of the memory bandwidth available with AMD Versal Premium Series Gen 2 devices [CXL 3.1 plus LPDDR5X memory] versus comparable competitive devices with LPDDR5 memory alone. Memory bandwidth will vary based on system configuration and other factors. (VER-059)

- Based on AMD internal analysis of Versal Premium Series Gen 2 devices with 400 Gb/s High-Speed Crypto Engines versus comparable competitive devices with 200 Gb/s crypto engines. Actual line rate speeds will vary based on system configuration and other factors. (VER-062)

- Based on an AMD internal analysis of the AMD Versal Premium Series Gen 2 device(s) with CXL 3.1 and PCIe 6.0 versus comparable competitive devices without CXL 3.1 and/or with PCIe Gen 4/5, as of July 2024. (VER-055)

- Based on AMD testing in January 2025, using the AMD Power Design Manager 2024.2 to estimate the total power consumption of a single 18x12 AXI crossbar design with 24 transceivers, synthesized and implemented with Vivado Design Suite 2024.2, on the Versal Prime Series VM1402 device with the programmable NoC, versus the total power consumption of the same single design, synthesized and implemented with Altera Quartus 24.1, on the Altera Agilex 7 AGFB023 device with open-source AXI soft IP and estimated with Altera Quartus Power Thermal Calculator 24.2. Results assume a fixed junction temperature (ΘJC) of 100°C and maximum process leakage devices. Results will vary based on architecture, device, customer design specifications, system configuration, and other factors. (VER-090)

- Based on an AMD internal analysis comparing the theoretical processing capability (including hard IP, AI Engines, and DSP) of the Versal RF Series VR19xx devices versus the largest Altera Agilex 9 Direct RF-Series ARGW027 device. Results may vary based on device, design, configuration, and other factors. (VER-072)

- Based on the projected combined total DMIPs of the Versal AI Edge Series Gen 2 and Versal Prime Series Gen 2 processing systems when configured with 8 Arm Cortex-A78AE applications cores @2.2 GHz & 10 Arm Cortex-R52 real-time cores @1.05 GHz, compared to the published combined total DMIPs of the processing systems in the first generation Versal AI Edge Series and Versal Prime Series. Versal AI Edge Series Gen 2 and Prime Series Gen 2 operating conditions: Highest available speed grade, 0.88V PS operating voltage, split-mode operation, maximum supported operating frequency. First generation Versal AI Edge Series and Prime Series operating conditions: Highest available speed grade, 0.88V PS operating voltage, maximum supported operating frequency. Actual DMIPs performance will vary when final products are released in market. (VER-027)

- TOPS/watt is based on AMD internal performance and power projections for the AIE-ML v2 compute tile architecture in the Versal AI Edge Series Gen 2 using the MX6 data type, compared to performance specifications and AMD Power Design Manager power results for the AIE-ML compute tile architecture featured in the first generation Versal AI Edge Series using the INT8 data type. Operating conditions: 1 GHz FMAX, 0.7V AIE operating voltage, 100°C junction temperature, typical process, 60% vector load, % activations = 0 < 10%. Actual performance will vary when final products are released in market. (VER-023)

- Based on AMD testing in January 2025, measuring the DDR read and write latency of a single multi-manager bridge design, implemented with AMD Vivado Design Suite 2024.1 and the AMD Versal Premium Series VP1202 device using the programmable NoC, versus the same design implemented with Altera Quartus 24.1, on the Altera Agilex 7 AGFB027 device using open-source AXI soft IP. Results will vary based on architecture, device, customer design specifications, system configuration, and other factors. (VER-086)

- Based on AMD testing in January 2025, comparing the post-implementation logic resource utilization of a single 18x12 AXI crossbar design with 24 transceivers, using the AMD Versal Prime Series VM1402 device with the programable NoC, implemented with AMD Vivado 2024.1 versus the Altera Agilex 7 AGFB023 device with open-source AXI soft IP, implemented with Altera Quartus 24.1. Results will vary based on architecture, device, customer design specifications, system configuration, and other factors. (VER-085)

- Based on AMD analysis in January 2025, summing the synthesis and implementation build times of a single 12x12 AXI crossbar design implemented with AMD Vivado 2024.2 on the AMD Versal Prime Series VM1402 device with the programmable NoC, versus the same design implemented with Altera Quartus 24.1, on the Altera Agilex AGFB023 device with open-source AXI soft IP. Results will vary based on architecture, device, customer design specifications, system configuration, and other factors. (VER-088)

- Based on AMD internal analysis in January 2025, using the AMD device and package thermal model to compare the JEDEC two-resistor thermal resistance Junction-to-Case (ΘJC) of the Versal Prime Series VM1802 device in a Versal VFVC1760 lidded package, versus the JEDEC two-resistor thermal resistance Junction-to-Case (ΘJC) of the same device in a Versal VSVD1760 lidless package with a stiffener ring. Results will vary based on architecture, device, customer design specifications, system configuration, and other factors. (VER-087)

- Based on AMD internal analysis of the memory bandwidth available with AMD Versal Premium Series Gen 2 devices [CXL 3.1 plus LPDDR5X memory] versus comparable competitive devices with LPDDR5 memory alone. Memory bandwidth will vary based on system configuration and other factors. (VER-059)

- Based on AMD internal analysis of Versal Premium Series Gen 2 devices with 400 Gb/s High-Speed Crypto Engines versus comparable competitive devices with 200 Gb/s crypto engines. Actual line rate speeds will vary based on system configuration and other factors. (VER-062)

- Based on an AMD internal analysis of the AMD Versal Premium Series Gen 2 device(s) with CXL 3.1 and PCIe 6.0 versus comparable competitive devices without CXL 3.1 and/or with PCIe Gen 4/5, as of July 2024. (VER-055)