Design Flow Assistant

Interactive guide to help you create a development strategy.

Wideband Spectrum. Massive DSP Compute. Single Chip.

Enables flexible, precise, and fast signal analysis over a wide observable spectrum for radar, spectral analysis, and test & measurement applications

Select, highly used, DSP functions are implemented in hard IP blocks, significantly reducing the amount of programmable logic utilization and power consumption, and accelerating processing time

Provides fast data processing with optimized size, weight, and power (SWaP), crucial for advanced signal processing applications

Harness the highest-resolution integrated RF sampling converters in a single-chip adaptive SoC with programmable logic.1

The monolithic AMD Versal™ RF adaptive SoC provides high-performance compute for the demanding DSP workloads of the modern aerospace and defense and advanced test and measurement markets—in a single device that meets SWaP requirements.

See the data sheet overview for the available feature combinations per device/package.

AMD Versal™ RF Series leverages the benefits of the Versal architecture, such as NoC, AI Engines, programmable logic, and flexible DDR—and adds 18 GHz direct RF-ADCs and RF-DACs for wideband-spectrum observability and dedicated hard IP cores in a monolithic die to meet aggressive SWaP requirements for A&D and test and measurement applications. The hard IP blocks include 4 GSPS FFT/iFFT, channelizers, a polyphase arbitrary resampler, and an updated LDPC decoder that supports DVB-S/S2x codes.

See the data sheet overview for the available feature combinations per device/package.

Versal RF Series devices include 14-bit RF-ADCs and RF-DACs, with calibration, that operate up to an input and output frequency of 18 GHz. The RF-DAC samples up to 16 GSPS while the RF-ADC supports both 8 GSPS and 32 GSPS configurations, providing wide-observable spectrum. Frequency agility is provided via integrated coarse and fine mixers and configurable decimation/interpolation. Several combinations of RF-DACs and RF-ADCs are supported, such as 16 RF-DACs and 16 RF-ADCs @ 8 GSPS, 8 RF-DACs and 4 RF-ADCs @ 32 GSPS, and 16 RF-DACS and 8 RF-ADCs @ 32 GSPS in compatible packages enabling scalable solutions.

Implementing highly used functions in hard IP blocks reduces dynamic power by up to 80% over an AMD soft logic implementation2 and occupies less physical area, resulting in lower overall size, weight, and power (SWaP). The dedicated IP included in Versal RF Series is configurable for common use cases and can dramatically reduce programmable logic (PL) and DSP Engines needed in a typical design. The Versal RF Series has multiple instances of the following hard IP blocks:

FFT/iFFT

A configurable 8-pt to 4K-pt, 4 GSPS hard FFT/iFFT block enables fast spectrum analysis of the input signals. If larger point size FFTs are needed, multiple instances of the hard FFT/iFFT block can be combined with the PL.

Channelizer

A polyphase filter bank channelizer separates wideband input spectrum into narrow subchannels, enabling fast identification and characterization of input signals. Multiple channelizer IP instances can be cascaded to increase resolution and accuracy of signal characterization. The hard channelizer IP block can also be used in reverse as a synthesizer. Additionally, channelizer IP can be used as a generic filter if the channelizer function (16-point FFT/iFFT) is not used.

LDPC Decoder

An updated version of the SD-FEC in Zynq™ RFSoC Gen 1 and Gen 3 is included in Versal RF Series devices. This variant of the SD-FEC only supports LDPC decoding, but adds the DVB-S2/S2X satellite codes supporting space applications. Use of this hard block significantly reduces the LUTs for systems using LDPC forward error correction, resulting in far lower power consumption. Note: Turbo codes and LDPC encoding are not supported in the dedicated IP but are available as soft IP cores.

Polyphase Arbitrary Resampler

A hard polyphase arbitrary resampler IP block (1 ≤ R ≤ 2) is provided for test & measurement applications. This hard IP block can also be used for general filtering.

Versal RF Series contains a dual-core Arm Cortex-A72 application processor and a dual-core Arm Cortex-R5F real-time processor to support diverse application needs. The application processing unit is ideal for complex applications supported by an OS, and the real-time processing unit is ideal for applications which need low latency, determinism, and real-time control. A third, and separate, platform management controller manages system boot, security, and debug.

Programmable logic enables the development of custom computational blocks for ever-changing algorithms. Loaded with a wide variety of memory elements and tightly coupled with programmable I/O, the programmable logic allows users to create powerful accelerators for any application.

High-performance X5IO with MIPI D-PHY at up to 4.5 Gb/s and C-PHY at up to 10 Gb/s support provide flexibility, real-time processing, and future adaptability.

Enhanced DSP Engines provide support for new operations and data types, including single and half-precision floating-point and complex 18x18 operations. With backward compatibility for AMD UltraScale+™ device designs, users can continue to leverage existing libraries and IP or update their designs to capture the improved compute performance enabled by this new architecture.

The AI Engine in Versal RF Series adaptive SoCs is a first-generation AI Engine optimized for real-time DSP computation and provides deterministic performance.

Hard DDR memory controllers support DDR5-6400 and LPDDR5X-8533 memory types with new inline crypto functionality—offering up to 136.5 GB/s memory bandwidth.

Learn how the Versal RF Series with RF-ADCs, RF-DACs, and hard IP blocks can provide a single-chip solution for your RF system at much lower SWaP.

Electromagnetic Spectrum Operations (EMSO) are becoming increasingly more challenging as the spectrum becomes more congested and contested. The Versal RF Series helps to address capabilities for EMSO in a highly optimized monolithic SWaP-efficient device. With 32 GSPS data converters supporting up to Ku Band and new hard IP blocks, the Versal RF Series integrates the capabilities of a Zynq UltraScale+ RFSoC and the high-DSP count of the Versal Premium Series into a single Versal RF Series device.

With monolithically integrated, advanced DSP compute, and high resolution 14-bit data converters sampling at 32 GSPS up to 18 GHz, the AMD Versal RF Series supports a broad range of test & measurement applications across semiconductor ATE, aerospace and defense, benchtop instruments, and 6G.

| VR1602 | VR1652 | VR1902 | VR1952 | ||

| 14-bit RF- ADC | # of ADCs | 16 | 4 | 16 | 8 |

| Max Sample Rate (GSPS) | 8 | 32 | 8 | 32 | |

| 14-bit RF-DAC | # of DACs | 16 | 8 | 16 | 16 |

| Max Sample Rate (GSPS) | 16 | 16 | 16 | 16 |

| VR1602 | VR1652 | VR1902 | VR1952 | |

| AI Engine Tiles | 126 | 126 | 120 | 120 |

| LDPC Decoder | 4 | 4 | - | - |

| Channelizer | 224 | 224 | 320 | 320 |

| FFT/iFFT | 28 | 28 | 40 | 40 |

| Polyphase Arbitrary Resampler | - | - | 8 | 8 |

| VR1602 | VR1652 | VR1902 | VR1952 | |

| Application Processing Unit | Application Processing Unit Dual-core Arm® Cortex®-A72, 48 KB/32 KB L1 Cache w/ parity & ECC; 1 MB L2 Cache w/ ECC | |||

| Real-Time Processing Unit | Real-Time Processing Unit Dual-core Arm Cortex-R5F, 32 KB/32 KB L1 Cache, and 256 KB TCM w/ECC | |||

| Memory | Memory 256 KB On-Chip Memory w/ECC | |||

| Connectivity | Connectivity Ethernet (x2); UART (x2); CAN-FD (x2); USB 2.0 (x1); SPI (x2); I2C (x2) | |||

| VR1602 | VR1652 | VR1902 | VR1952 | |

| System Logic Cells | 1,205,400 | 1,205,400 | 2,473,800 | 2,473,800 |

| LUTs | 551,040 | 551,040 | 1,130,880 | 1,130,880 |

| DSP58 | 2,256 | 2,256 | 3,976 | 3,976 |

| VR1602 | VR1652 | VR1902 | VR1952 | |

| Total PL Memory (Mb) | 156 | 156 | 189 | 189 |

| DDR Memory Controllers | 4 | 4 | 4 | 4 |

| GTYP Transceivers | 12 | 12 | - | - |

| GTM Transceivers (56G (112G)) | 8 (4) | 8 (4) | - | - |

| GTMP Transceivers (56G (112G)) | - | - | 20 (10) | 20 (10) |

| 100G Multi-rate Ethernet MAC | 2 | 2 | 2 | 2 |

| 600G Ethernet MAC | - | - | 3 | 3 |

| PL PCIe (Gen5x4) | 1 | 1 | 1 | 1 |

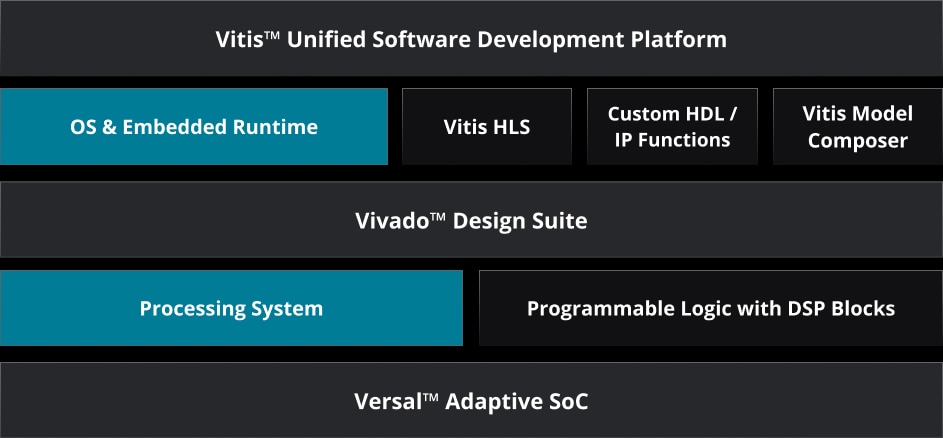

AMD provides a leading software development environment for designing with adaptive SoCs and FPGAs—this includes tools (compilers, simulators, etc.), IP, and solutions.

This environment can reduce development time while allowing developers to achieve high performance per watt. These tools enable all types of developers from application and algorithm engineers, embedded software developers, and traditional hardware developers to use AMD adaptive computing solutions.

The Versal RF Series is currently in Early Access. Contact your local AMD sales representative to apply for the Early Access program or visit the Contact Sales page.

Join the Versal adaptive SoC notification list to receive the latest news and updates.

Based on AMD internal analysis to calculate the theoretical DSP compute (including hard IP, AI Engines, and DSP) in channelizer mode offered by the Versal RF Series devices vs. the published DSP compute of the previous-generation Zynq UltraScale+ RFSoC Gen 3, as of September 2024. Actual results will vary based on configuration, device, design, and other factors. (VER-068)

Based on an AMD engineering projection of hard IP power values, November 2024. AMD Power Design Manager (2023.2.2) used to determine total power of soft logic, based on Vivado 2023.2.2 IP catalog. (VER-074)

Based on an AMD internal analysis in November 2024, to compare the amount of DSP processing, AI Engine compute, and RF sampling converter capabilities offered by one (1) Versal RF VR1652 device (single chip) vs. that of four (4) Virtex UltraScale+ VU13P devices + one (1) Versal AI Core Series VC1702 device + one (1) ADI discrete AD9084 RF converter. Results will vary based on device, design, configuration, and other factors. (VER-077)

Tera operations per second (TOPS) for an AMD Versal RF Series device is the maximum number of operations per second that can be executed in an optimal scenario and may not be typical. TOPS will vary based on device, design, configuration, and other factors. (VER-084)