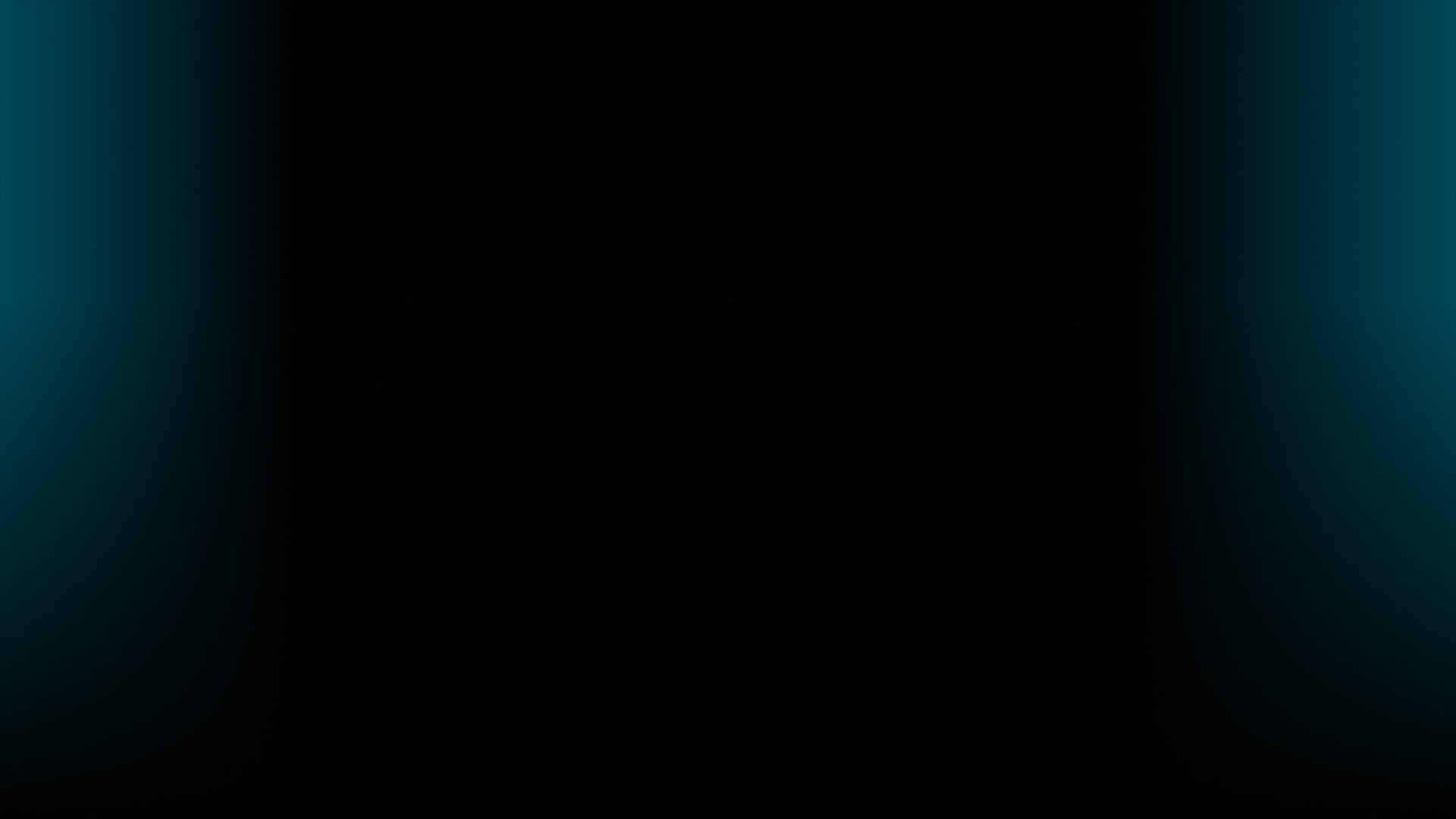

Übersicht

Genaue Breitbandspektrum-Überwachbarkeit

Ermöglicht eine flexible, genaue und schnelle Signalanalyse über ein breites überwachbares Spektrum für Radar, Spektralanalyse sowie Test- und Messanwendungen

Enormes DSP-Computing

Ausgewählte, stark genutzte DSP-Funktionen werden in Hard-IP-Blöcken implementiert, was die Auslastung der programmierbaren Logik und den Stromverbrauch signifikant senkt und die Verarbeitungszeit beschleunigt

SWaP-optimiert

Bietet eine schnelle Datenverarbeitung mit optimierter Größe, Gewicht und Stromverbrauch (SWaP: Size, Weight and Power), was für erweiterte Signalverarbeitungsanwendungen wichtig ist

RF-Signalverarbeitung optimieren

Nutzen Sie die integrierten RF-Abtastkonverter mit höchster Auflösung in einem adaptiven Single-Chip-SoC mit programmierbarer Logik.1

Das monolithische adaptive AMD Versal™ RF SoC bietet High-Performance-Computing für anspruchsvolle DSP-Auslastungen der modernen Verteidigungs-, Luft- und Raumfahrtindustrie sowie der erweiterten Test- und Messmärkte – in einem einzigen Gerät, das SWaP-Anforderungen erfüllt.

Produktvorteile

Siehe die Datenblattübersicht für die verfügbaren Kombinationen pro Gerät/Paket.

Massives DSP-Computing an der RF Edge

Die AMD Versal™ RF-Serie nutzt die Vorteile der Versal Architektur, wie z. B. NoC, KI-Engines, programmierbare Logik und flexible DDR – und erweitert diese durch 18 GHz Direkt-RF-ADCs und RF-DACs für Breitbandspektrum-Überwachbarkeit und dedizierte Hard-IP-Kerne in einem monolithischen Mikrochip, um die aggressiven SWaP-Anforderungen für Verteidigung, Luft- und Raumfahrt sowie Test- und Messanwendungen zu erfüllen. Die Hard-IP-Blöcke umfassen 4 GSPS FFT/iFFT, Channelizer, einen mehrphasigen Arbitrary Resampler und einen aktualisierten LDPC-Dekodierer, der DVB-S/S2x-Codes unterstützt.

Hauptmerkmale

Siehe die Datenblattübersicht für die verfügbaren Kombinationen pro Gerät/Paket.

Direkt-RF-ADCs und RF-DACs

Versal RF-Serie Geräte umfassen 14-Bit-RF-ADCs und RF-DACs mit Kalibrierung, die bis zu einer Eingangs- und Ausgangsfrequenz von 18 GHz arbeiten. Das RF-DAC tastet bis zu 16 GSPS ab, während das RF-ADC Konfigurationen mit sowohl 8 GSPS als auch 32 GSPS unterstützt. Dies ermöglicht ein breites, beobachtbares Spektrum. Frequenzflexibilität wird über integrierte Grob- und Feinmischer und konfigurierbare Dezimierung/Interpolation bereitgestellt. Es werden mehrere Kombinationen von RF-DACs und RF-ADCs unterstützt, z. B. 16 RF-DACs und 16 RF-ADCs bei 8 GSPS, 8 RF-DACs und 4 RF-ADCs bei 32 GSPS und 16 RF-DACs und 8 RF-ADCs bei 32 GSPS in kompatiblen Paketen, die skalierbare Lösungen ermöglichen.

Hard-IP-Blöcke für Signalverarbeitung

Die Implementierung von stark verwendeten Funktionen in Hard-IP-Blöcken senkt den dynamischen Stromverbrauch um bis zu 80 % im Vergleich zu einer AMD Implementierung mit weicher Logik2 und belegt weniger physische Stellfläche, was zu geringerer Gesamtgröße, geringerem Gewicht und geringerem Stromverbrauch führt (SWaP). Die dedizierte IP in der Versal RF-Serie ist für gängige Anwendungsfälle konfigurierbar und kann die programmierbare Logik (PL) und die in einem typischen Konzept erforderlichen DSP-Engines deutlich reduzieren. Die Versal RF-Serie hat mehrere Instanzen der folgenden Hard-IP-Blöcke:

FFT/iFFT

Ein konfigurierbarer 8-pt bis 4K-pt, 4 GSPS Hard-FFT/iFFT-Block ermöglicht eine schnelle Spektrumanalyse der Eingangssignale. Sollten FFTs mit größerer Punktgröße erforderlich sein, können mehrere Instanzen des Hard-FFT/iFFT-Blocks mit der PL kombiniert werden.

Channelizer

Ein mehrphasiger Filterbank-Channelizer unterteilt das Breitband-Eingangsspektrum in schmale Unterkanäle, was eine schnelle Identifizierung und Charakterisierung der Eingangssignale ermöglicht. Mehrere Channelizer-IP-Instanzen können kaskadiert werden, um die Auflösung und Genauigkeit der Signalcharakterisierung zu erhöhen. Der Hard-Channelizer-IP-Block kann umgekehrt auch als Synthesizer verwendet werden. Außerdem kann die Channelizer-IP als generischer Filter eingesetzt werden, wenn die Channelizer-Funktion (16-Punkt-FFT/iFFT) nicht genutzt wird.

LDPC-Decoder

Eine aktualisierte Version der SD-FEC in Zynq™ RFSoC der 1. und 3. Generation ist in Versal RF-Serie Geräten enthalten. Diese Variante der SD-FEC unterstützt nur die LDPC-Dekodierung, fügt jedoch die DVB-S2/S2X Satellitencodes zur Unterstützung von Raumfahrtanwendungen hinzu. Der Einsatz dieses Hard-Blocks reduziert deutlich die LUTs für Systeme mit LDPC-Vorwärtsfehlerkorrektur, was zu einem deutlich geringeren Stromverbrauch führt. Hinweis: Turbo-Codes und LDPC-Kodierung werden in der dedizierten IP nicht unterstützt, sind aber als Soft-IP-Kerne verfügbar.

Mehrphasiger Arbitrary Resampler

Ein Hard-IP-Block mit mehrphasigem Arbitrary Resampler (1 ≤ R ≤ 2) wird für Test- und Messanwendungen bereitgestellt. Dieser Hard-IP-Block kann auch für allgemeines Filtern verwendet werden.

Verarbeitungssystem

Die Versal RF-Serie enthält einen Dual-Core Arm Cortex-A72 Anwendungsprozessor und einen Dual-Core Arm Cortex-R5F Echtzeitprozessor zur Unterstützung verschiedener Anwendungsanforderungen. Die Anwendungsverarbeitungseinheit ist ideal für von einem Betriebssystem unterstützte komplexe Anwendungen, und die Echtzeitverarbeitungseinheit eignet sich hervorragend für Anwendungen, die niedrige Latenz, Determinismus und Echtzeitsteuerung erfordern. Über einen dritten und separaten Plattform-Management-Controller werden Systemstart, Sicherheit und Fehlersuche verwaltet.

Programmierbare Logik und E/A

Die programmierbare Logik ermöglicht die Entwicklung benutzerdefinierter Berechnungsblöcke für sich ständig ändernde Algorithmen. Ausgestattet mit einer Vielzahl an Speicherelementen und eng gekoppelt mit programmierbarem E/A ermöglicht die programmierbare Logik den Benutzern, leistungsstarke Beschleuniger für beliebige Anwendungen zu erstellen.

High-Performance-X5IO mit MIPI D-PHY mit bis zu 4,5 Gb/s und C-PHY mit bis zu 10 Gb/s bieten Flexibilität, Verarbeitung in Echtzeit und Anpassungsfähigkeit an zukünftige Entwicklungen.

DSP-Engines

Erweiterte DSP-Engines bieten Unterstützung für neue Vorgänge und Datentypen, u. a. einfache und halbgenaue Gleitkomma- und komplexe 18 x 18-Vorgänge. Mithilfe der Rückwärtskompatibilität für AMD UltraScale+™ Gerätedesigns können Benutzer bestehende Bibliotheken und IP weiterhin nutzen oder ihre Designs aktualisieren, um die durch diese neue Architektur ermöglichte verbesserte Rechnerleistung zu erfassen.

Versal AI Engines

Die KI-Engine in adaptiven Versal RF-Serie SoCs ist eine KI-Engine der ersten Generation, die für DSP-Berechnung in Echtzeit optimiert ist und deterministische Performance bietet.

DDR5 und LPDDR5

Hardware-DDR-Speicher-Controller unterstützen DDR5-6400 und LPDDR5X-8533 Speichertypen mit der neuen Inline-Kryptofunktionalität und bieten eine Speicherbandbreite von bis zu 136,5 GB/s.

Weitere Informationen zu den Funktionen der adaptiven Versal SoCs

Adaptives Versal RF-Serie SoC – Produktübersicht

Erfahren Sie, wie die Versal RF-Serie mit RF-ADCs, RF-DACs und Hard-IP-Blöcken eine Single-Chip-Lösung für Ihr RF-System mit deutlich geringerem SWaP bereitstellen kann.

Anwendungen und Branchen

Electromagnetic Spectrum Operations für Verteidigung, Luft- und Raumfahrt voranbringen

Electromagnetic Spectrum Operations (EMSO, Operationen im elektromagnetischen Spektrum) werden immer schwieriger, da das Spektrum zunehmend überlastet und umkämpft ist. Die Versal RF-Serie trägt dazu bei, Fähigkeiten für EMSO in einem hochgradig optimierten monolithischen SWaP-effizienten Gerät anzusprechen. Mit 32 GSPS Datenkonvertern, die bis zu Ku-Band und neue Hard-IP-Blöcke unterstützen, integriert die Versal RF-Serie die Fähigkeiten eines Zynq UltraScale+ RFSoC und die hohe DSP-Anzahl der Versal Premium-Serie in ein einziges Versal RF-Serie Gerät.

Breitband-Signalanalyselösungen mit adaptiven AMD Versal RF-Serie SoCs

Die AMD Versal RF-Serie verfügt über monolithisch integrierte, erweiterte DSP-Computing- und hochauflösende 14-Bit-Datenkonverter, die bei 32 GSPS bis zu 18 GHz abtasten, und unterstützt ein breites Spektrum an Test- und Messanwendungen für Halbleiter-ATE, Verteidigung, Luft- und Raumfahrt, Benchtop-Instrumente und 6G.

Produkt-Spezifikationen

RF-Datenkonverter

| VR1602 | VR1652 | VR1902 | VR1952 | ||

| 14-Bit RF-ADC | Anzahl der ADCs | 16 | 4 | 16 | 8 |

| Max. Abtastrate (GSPS) | 8 | 32 | 8 | 32 | |

| 14-Bit RF-DAC | Anzahl der DACs | 16 | 8 | 16 | 16 |

| Max. Abtastrate (GSPS) | 16 | 16 | 16 | 16 |

KI-Engines und Hard-IP-Funktionen

| VR1602 | VR1652 | VR1902 | VR1952 | |

| KI-Engine-Kacheln | 126 | 126 | 120 | 120 |

| LDPC-Decoder | 4 | 4 | – | – |

| Channelizer | 224 | 224 | 320 | 320 |

| FFT/iFFT | 28 | 28 | 40 | 40 |

| Mehrphasiger Arbitrary Resampler | – | – | 8 | 8 |

Funktionen des Verarbeitungssystems

| VR1602 | VR1652 | VR1902 | VR1952 | |

| Anwendungsverarbeitungseinheit | Anwendungsverarbeitungseinheit Dual-Core Arm® Cortex®-A72, 48 KB/32 KB L1-Cache mit Parität und ECC; 1 MB L2-Cache mit ECC | |||

| Echtzeitverarbeitungseinheit | Echtzeitverarbeitungseinheit Dual-Core Arm Cortex-R5F, 32 KB/32 KB L1-Cache und 256 KB TCM mit ECC | |||

| Speicher | Speicher 256 KB On-Chip-Memory mit ECC | |||

| Konnektivität | Konnektivität Ethernet (x2); UART (x2); CAN-FD (x2); USB 2.0 (x1); SPI (x2); I2C (x2) | |||

Funktionen der programmierbaren Logik

| VR1602 | VR1652 | VR1902 | VR1952 | |

| Systemlogikzellen | 1.205.400 | 1.205.400 | 2.473.800 | 2.473.800 |

| LUTs | 551.040 | 551.040 | 1.130.880 | 1.130.880 |

| DSP58 | 2.256 | 2.256 | 3.976 | 3.976 |

Speicher, Transceiver und Schnittstelle

| VR1602 | VR1652 | VR1902 | VR1952 | |

| PL-Speicher insgesamt (MB) | 156 | 156 | 189 | 189 |

| DDR-Speicher-Controller | 4 | 4 | 4 | 4 |

| GTYP-Transceiver | 12 | 12 | – | – |

| GTM-Transceiver (56G (112G)) | 8 (4) | 8 (4) | – | – |

| GTMP-Transceiver (56G (112G)) | – | – | 20 (10) | 20 (10) |

| 100G Multi-Rate-Ethernet-MAC | 2 | 2 | 2 | 2 |

| 600G Ethernet-MAC | – | – | 3 | 3 |

| PL-PCIe (Gen5x4) | 1 | 1 | 1 | 1 |

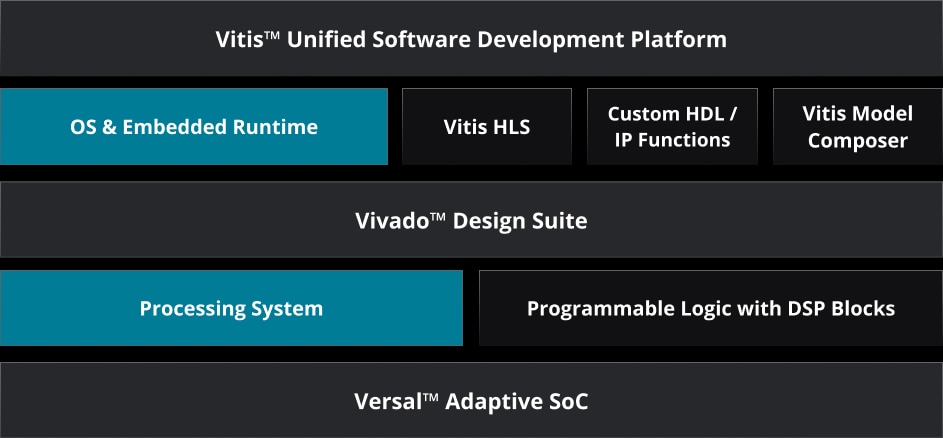

Für alle Entwickler

AMD präsentiert die führende Softwareentwicklungsumgebung für Konstruktionen mit adaptiven SoCs und FPGAs. Die Plattform umfasst Tools (Compiler, Simulatoren usw.), IP und Lösungen.

Diese Umgebung hilft, die Entwicklungszeit zu verkürzen, und ermöglicht es Ihren Konstrukteuren, eine höhere Performance pro Watt zu erzielen. Diese Tools sind unverzichtbar für alle Entwickler, die mit adaptiven Computing-Lösungen von AMD arbeiten – Anwendungstechniker und Algorithmusinformatiker, Embedded Software-Entwickler und Konstrukteure traditioneller Hardware.

Ressourcen

Programm für frühzeitigen Zugriff

Die Versal RF-Serie ist derzeit im Programm für frühzeitigen Zugriff enthalten. Kontaktieren Sie den AMD Vertrieb vor Ort, um sich für das Programm für frühzeitigen Zugriff zu bewerben, oder besuchen Sie die Seite „Vertrieb kontaktieren“.

Immer informiert bleiben

Melden Sie sich für die E-Mail-Liste an, um die neuesten Nachrichten und Meldungen zu adaptiven Versal SoCs zu erhalten.

Fußnoten

- Basierend auf einer internen Analyse von AMD, zum Vergleich der Spezifikation für die ADC-Abtastrate (GSPS) der Versal RF VR1652 und VR1952 Geräte gegenüber den veröffentlichten Spezifikationen der Intel Agilex 9 Direct RF-Serie AGRW014 und AGRW027 FPGAs und den Konzeptspezifikationen für die Vorabversion der ADI Apollo AD9084 und AD9088 Geräte. (VER-075)

- Basierend auf technischen Prognosen von AMD im November 2024 unter Verwendung der Hard-IP-Funktionen in Versal RF-Serie Geräten zur Messung der dynamischen Leistung im Vergleich zur Berechnung der Gesamtleistung einer Implementierung von AMD mit weicher Logik, gemessen mit dem AMD Power Design Manager (2023.2.2), auf Basis des AMD Vivado 2023.2.2 IP-Katalogs. (VER-080)

Basierend auf einer internen Analyse von AMD zur Berechnung des theoretischen DSP-Computing (einschließlich Hard-IP, KI-Engines und DSP) im Channelizer-Modus der Versal RF-Serie Geräte im Vergleich zum veröffentlichten DSP-Computing des Zynq UltraScale+ RFSoC der vorherigen 3. Generation im September 2024. Tatsächliche Ergebnisse können je nach Konfiguration, Gerät, Konzept und anderen Faktoren abweichen. (VER-068)

Basierend auf einer technischen Projektion der Hard-IP-Leistungswerte von AMD (November 2024). AMD Power Design Manager (2023.2,2) zur Bestimmung der Gesamtleistung der Soft Logic basierend auf dem Vivado 2023.2.2 IP-Katalog. (VER-074)

Basierend auf einer internen Analyse von AMD im November 2024 zum Vergleich des Umfangs der Fähigkeiten für DSP-Verarbeitung, KI-Engine-Computing und RF-Abtastkonverter, die von einem (1) Versal RF VR1652 Gerät (Single Chip) bzw. von vier (4) Virtex UltraScale+ VU13P Geräten + einem (1) Versal AI Core-Serie VC1702 Gerät + einem (1) diskreten ADI AD9084 RF-Konverter bereitgestellt werden. Die Ergebnisse können je nach Gerät, Design, Konfiguration und anderen Faktoren abweichen. (VER-077)

Tera of Operations per Second (TOPS – Billionen Operationen pro Sekunde) für einen Versal RF-Serie Chip gibt die maximale Anzahl an Operationen pro Sekunde an, die in einem optimalen Szenario ausgeführt werden können, und entspricht möglicherweise nicht der typischen Leistung. TOPS können je nach Gerät, Design, Konfiguration und anderen Faktoren abweichen. (VER-084)

- Basierend auf einer internen Analyse von AMD, zum Vergleich der Spezifikation für die ADC-Abtastrate (GSPS) der Versal RF VR1652 und VR1952 Geräte gegenüber den veröffentlichten Spezifikationen der Intel Agilex 9 Direct RF-Serie AGRW014 und AGRW027 FPGAs und den Konzeptspezifikationen für die Vorabversion der ADI Apollo AD9084 und AD9088 Geräte. (VER-075)

- Basierend auf technischen Prognosen von AMD im November 2024 unter Verwendung der Hard-IP-Funktionen in Versal RF-Serie Geräten zur Messung der dynamischen Leistung im Vergleich zur Berechnung der Gesamtleistung einer Implementierung von AMD mit weicher Logik, gemessen mit dem AMD Power Design Manager (2023.2.2), auf Basis des AMD Vivado 2023.2.2 IP-Katalogs. (VER-080)

Basierend auf einer internen Analyse von AMD zur Berechnung des theoretischen DSP-Computing (einschließlich Hard-IP, KI-Engines und DSP) im Channelizer-Modus der Versal RF-Serie Geräte im Vergleich zum veröffentlichten DSP-Computing des Zynq UltraScale+ RFSoC der vorherigen 3. Generation im September 2024. Tatsächliche Ergebnisse können je nach Konfiguration, Gerät, Konzept und anderen Faktoren abweichen. (VER-068)

Basierend auf einer technischen Projektion der Hard-IP-Leistungswerte von AMD (November 2024). AMD Power Design Manager (2023.2,2) zur Bestimmung der Gesamtleistung der Soft Logic basierend auf dem Vivado 2023.2.2 IP-Katalog. (VER-074)

Basierend auf einer internen Analyse von AMD im November 2024 zum Vergleich des Umfangs der Fähigkeiten für DSP-Verarbeitung, KI-Engine-Computing und RF-Abtastkonverter, die von einem (1) Versal RF VR1652 Gerät (Single Chip) bzw. von vier (4) Virtex UltraScale+ VU13P Geräten + einem (1) Versal AI Core-Serie VC1702 Gerät + einem (1) diskreten ADI AD9084 RF-Konverter bereitgestellt werden. Die Ergebnisse können je nach Gerät, Design, Konfiguration und anderen Faktoren abweichen. (VER-077)

Tera of Operations per Second (TOPS – Billionen Operationen pro Sekunde) für einen Versal RF-Serie Chip gibt die maximale Anzahl an Operationen pro Sekunde an, die in einem optimalen Szenario ausgeführt werden können, und entspricht möglicherweise nicht der typischen Leistung. TOPS können je nach Gerät, Design, Konfiguration und anderen Faktoren abweichen. (VER-084)