Asistente de flujo de diseño

Guía interactiva para ayudarte a crear una estrategia de desarrollo.

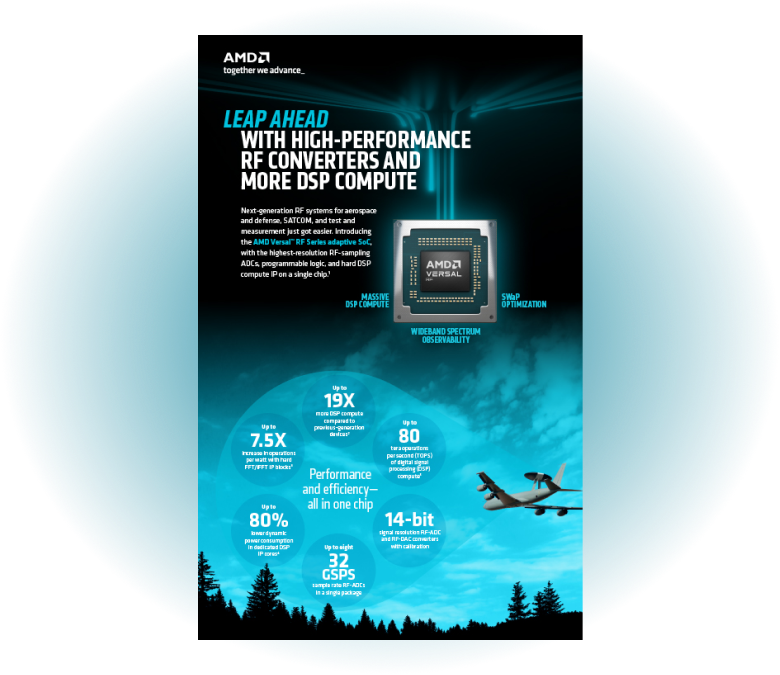

Espectro de banda ancha. Procesamiento de DSP masivo. Chip único.

Permite un análisis de señales flexible, preciso y rápido en un amplio espectro observable para aplicaciones de radar, análisis espectral y prueba y medición

Las funciones de DSP selectas y muy utilizadas se implementan en bloques IP duros, lo que reduce significativamente la cantidad de utilización lógica programable y el consumo energético, y acelera el tiempo de procesamiento

Proporciona un procesamiento de datos rápido con un tamaño, peso y potencia (SWaP) optimizados, cruciales para aplicaciones de procesamiento de señal avanzadas

Aprovecha los convertidores de muestreo RF integrados de mayor resolución en un SoC adaptable de un solo chip con lógica programable.1

El SoC adaptable AMD Versal™ RF monolítico proporciona un procesamiento de alto rendimiento para las exigentes cargas de trabajo de DSP de los mercados aeroespacial y de defensa modernos, así como de pruebas y mediciones avanzadas, en un único dispositivo que cumple los requisitos de SWaP.

Consulte la descripción general de la hoja de datos para conocer las combinaciones de funciones disponibles por dispositivo/paquete.

La Serie AMD Versal™ RF aprovecha los beneficios de la arquitectura Versal, como NoC, motores de IA, lógica programable y DDR flexible, y agrega ADC RF y DAC RF directos de 18 GHz para observabilidad del espectro de banda ancha y núcleos IP duros dedicados, en un chip monolítico a fin de satisfacer los exigentes requisitos de SWaP para aplicaciones de A&D y de prueba y medición. Los bloques IP duros incluyen 4 GSPS FFT/iFFT, canalizadores, un remuestreo arbitrario polifásico y un decodificador LDPC actualizado que admite códigos DVB-S/S2X.

Consulte la descripción general de la hoja de datos para conocer las combinaciones de funciones disponibles por dispositivo/paquete.

Los dispositivos de la Serie Versal RF incluyen ADC RF y DAC RF de 14 bits, con calibración, que funcionan con una frecuencia de entrada y salida de hasta 18 GHz. El DAC RF muestrea hasta 16 GSPS, mientras que el ADC RF admite configuraciones de 8 GSPS y 32 GSPS, lo que proporciona un amplio espectro observable. La agilidad de la frecuencia se proporciona mediante mezcladores gruesos y finos integrados y decimación/interpolación configurable. Se admiten varias combinaciones de DAC RF y ADC RF, como 16 DAC RF y 16 ADC RF a 8 GSPS, 8 DAC RF y 4 ADC RF a 32 GSPS, y 16 DAC RF y 8 ADC RF a 32 GSPS en paquetes compatibles que permiten soluciones escalables.

La implementación de funciones muy utilizadas en bloques IP duros reduce la potencia dinámica hasta en un 80 % con respecto a una implementación de lógica suave de AMD2 y ocupa menos área física, lo que se traduce en una reducción del tamaño, el peso y la potencia (SWaP) totales. La IP dedicada incluida en la Serie Versal RF se puede configurar para casos de uso comunes y puede reducir drásticamente los motores de lógica programable (PL) y DSP necesarios en un diseño típico. La Serie Versal RF tiene varias instancias de los siguientes bloques de IP duros:

FFT/iFFT

Un bloque FFT/iFFT duro configurable de 8 a 4 K puntos y 4 GSPS permite un análisis rápido del espectro de las señales de entrada. Si se necesitan FFT de mayor tamaño de punto, se pueden combinar varias instancias del bloque FFT/iFFT duro con el PL.

Canalizador

Un canalizador de banco de filtros polifásicos separa el espectro de entrada de banda ancha en subcanales estrechos, lo que permite una identificación y caracterización rápidas de las señales de entrada. Se pueden conectar en cascada varias instancias de IP de canalizador para aumentar la resolución y la precisión de la caracterización de la señal. El bloque IP del canalizador físico también se puede utilizar en sentido inverso como sintetizador. Además, la IP del canalizador se puede utilizar como filtro genérico si no se utiliza la función del canalizador (FFT/iFFT de 16 puntos).

Decodificador LDPC

En los dispositivos de la Serie Versal RF se incluye una versión actualizada de SD-FEC en Zynq™ RFSoC de 1.ª y 3.ª generación. Esta variante del SD-FEC solo admite decodificación LDPC, pero agrega los códigos de satélite DVB-S2/S2X que admiten aplicaciones espaciales. El uso de este bloque duro reduce significativamente las LUT para sistemas que utilizan la corrección de errores hacia adelante de LDPC, lo que se traduce en un consumo energético mucho menor. Nota: Los códigos turbo y la codificación LDPC no son compatibles con la IP dedicada, pero están disponibles como núcleos IP suaves.

Remuestreo arbitrario polifásico

Se proporciona un bloque IP de remuestreo arbitrario polifásico duro (1 ≤ R ≤ 2) para aplicaciones de prueba y medición. Este bloque de IP duro también se puede utilizar para el filtrado general.

La Serie Versal RF contiene un procesador de aplicaciones Arm Cortex-A72 de doble núcleo y un procesador en tiempo real Arm Cortex-R5F de doble núcleo para satisfacer diversas necesidades de aplicación. La unidad de procesamiento de aplicaciones es ideal para aplicaciones complejas compatibles con un SO, y la unidad de procesamiento en tiempo real es perfecta para aplicaciones que necesitan una latencia baja, determinismo y control en tiempo real. Un tercer controlador de administración de plataforma independiente administra el inicio, la seguridad y la depuración del sistema.

La lógica programable permite el desarrollo de bloques computacionales personalizados para los algoritmos cambiantes. Con una amplia variedad de elementos de memoria y un estrecho acoplamiento con E/S programable, la lógica programable les permite a los usuarios crear potentes aceleradores para cualquier aplicación.

El X5IO de alto rendimiento con MIPI D-PHY de hasta 4,5 Gb/s y C-PHY de hasta 10 Gb/s proporcionan flexibilidad, procesamiento en tiempo real y adaptabilidad futura.

Los motores de DSP mejorados proporcionan compatibilidad para nuevas operaciones y tipos de datos, que incluye un punto flotante de precisión única y media, además de operaciones complejas de 18 x 18. Es compatible con versiones anteriores de los diseños de dispositivos AMD UltraScale+™. Los usuarios pueden seguir aprovechando las bibliotecas existentes e IP o actualizar los diseños para capturar el rendimiento informático mejorado que ofrece esta nueva arquitectura.

El motor de IA de los SoC adaptables de la Serie Versal RF es un motor de IA de primera generación optimizado para el cálculo de DSP en tiempo real y proporciona un rendimiento determinista.

Los controladores de memoria DDR (double-data rate, tasa de datos doble) más robustos admiten DDR5-6400 y LPDDR5X-8533 con la nueva funcionalidad de cifrado en línea, lo que ofrece un ancho de banda de memoria de hasta 136,5 Gb/s.

Descubre cómo la Serie Versal RF con ADC RF, DAC RF y bloques de IP duros puede proporcionar una solución de chip único para tu sistema RF con un SWaP mucho menor.

Las operaciones de espectro electromagnético (EMSO) son cada vez más difíciles a medida que el espectro se congestiona y disputa. La Serie Versal RF ayuda a abordar las capacidades de EMSO en un dispositivo monolítico altamente optimizado con eficiencia de SWaP. Con convertidores de datos de 32 GSPS que admiten hasta la banda Ku y nuevos bloques IP duros, la Serie Versal RF integra las capacidades de un RFSoC Zynq UltraScale+ y el alto recuento de DSP de la Serie Versal Premium en un único dispositivo de la Serie Versal RF.

Con procesamiento DSP avanzado e integrado monólicamente y convertidores de datos de 14 bits de alta resolución con muestreo a 32 GSPS hasta 18 GHz, la Serie AMD Versal RF admite una amplia gama de aplicaciones de prueba y medición en ATE de semiconductores, aeroespacial y de defensa, instrumentos de sobremesa y 6G.

| VR1602 | VR1652 | VR1902 | VR1952 | ||

| ADC RF de 14 bits | Cantidad de ADC | 16 | 4 | 16 | 8 |

| Velocidad de muestreo máxima (GSPS) | 8 | 32 | 8 | 32 | |

| DAC RF de 14 bits | Cantidad de DAC | 16 | 8 | 16 | 16 |

| Velocidad de muestreo máxima (GSPS) | 16 | 16 | 16 | 16 |

| VR1602 | VR1652 | VR1902 | VR1952 | |

| Mosaicos de motor de IA | 126 | 126 | 120 | 120 |

| Decodificador LDPC | 4 | 4 | - | - |

| Canalizador | 224 | 224 | 320 | 320 |

| FFT/iFFT | 28 | 28 | 40 | 40 |

| Remuestreo arbitrario polifásico | - | - | 8 | 8 |

| VR1602 | VR1652 | VR1902 | VR1952 | |

| Unidad de procesamiento de aplicaciones | Unidad de procesamiento de aplicaciones Arm® Cortex®-A72 de doble núcleo, caché L1 de 48 KB/32 KB con paridad y ECC; caché L2 de 1 MB con ECC | |||

| Unidad de procesamiento en tiempo real | Unidad de procesamiento en tiempo real Arm Cortex®-R5F de doble núcleo, caché L1 de 32 KB/32 KB y TCM de 256 KB con ECC | |||

| Memoria | Memoria en chip de 256 KB con ECC | |||

| Conectividad | Conectividad Ethernet (x2); UART (x2); CAN-FD (x2); USB 2.0 (x1); SPI (x2); I2C (x2) | |||

| VR1602 | VR1652 | VR1902 | VR1952 | |

| Células lógicas del sistema | 1 205 400 | 1 205 400 | 2 473 800 | 2 473 800 |

| LUTS | 551 040 | 551 040 | 1 130 880 | 1 130 880 |

| DSP58 | 2256 | 2256 | 3976 | 3976 |

| VR1602 | VR1652 | VR1902 | VR1952 | |

| Memoria PL total (MB) | 156 | 156 | 189 | 189 |

| Controladores de memoria DDR | 4 | 4 | 4 | 4 |

| Transceptores GTYP | 12 | 12 | - | - |

| TRANSCEPTORES GTM (56 G [112 G]) | 8 (4) | 8 (4) | - | - |

| Tranceptores GTM (56 G [112 G]) | - | - | 20 (10) | 20 (10) |

| MAC de Ethernet de velocidad múltiple de 100 G | 2 | 2 | 2 | 2 |

| MAC de Ethernet de 600 G | - | - | 3 | 3 |

| PL PCIe (Gen5 x4) | 1 | 1 | 1 | 1 |

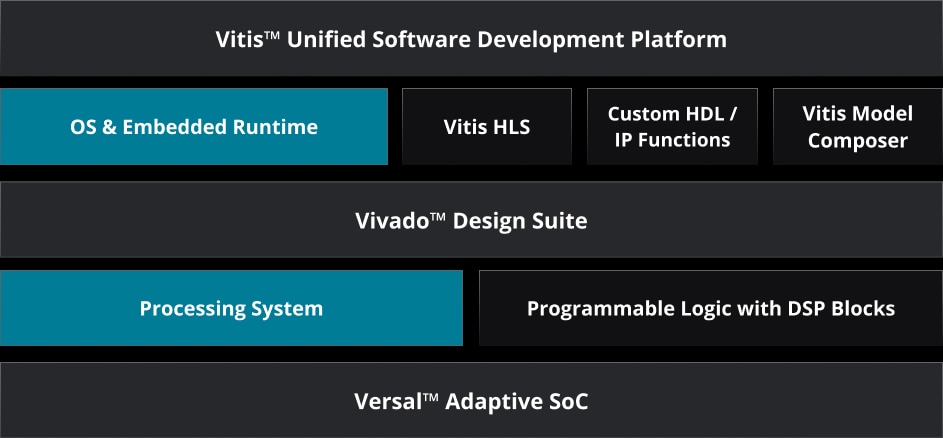

AMD proporciona un entorno de desarrollo de software líder para diseñar con SoC y FPGA adaptables, que incluye herramientas (compiladores, simuladores, etc.), IP y soluciones.

Este entorno puede reducir el tiempo de desarrollo y, al mismo tiempo, permitir que los desarrolladores logren un alto rendimiento por watt. Estas herramientas permiten que todo tipo de desarrolladores (los ingenieros de aplicaciones y algoritmos, los desarrolladores de software integrado y los desarrolladores de hardware tradicionales) utilicen soluciones informáticas adaptables de AMD.

La Serie Versal RF se encuentra actualmente en Early Access. Comunícate con tu representante de ventas local de AMD para solicitar el programa Early Access o visita la página Comunícate con el equipo de ventas.

Únete a la lista de notificaciones de SoC adaptable de Versal para recibir las noticias y actualizaciones más recientes.

Basado en el análisis interno de AMD para calcular el procesamiento teórico de DSP (incluidos IP dura, motores de IA y DSP) en modo canalizador ofrecido por los dispositivos de la Serie Versal RF frente al procesamiento de DSP publicado de la generación anterior de RFSoC Zynq UltraScale+ de 3.ª generación, al mes de septiembre del 2024. Los resultados reales variarán en función de la configuración, el dispositivo, el diseño y otros factores. (VER-068)

Basado en una proyección de ingeniería de AMD sobre valores de potencia de IP dura, noviembre del 2024. Se utilizó AMD Power Design Manager (2023.2.2) para determinar la potencia total de la lógica blanda, basado en el catálogo IP de Vivado 2023.2.2. (VER-074)

Basado en un análisis interno de AMD realizado en noviembre de 2024, para comparar la cantidad de procesamiento DSP, el procesamiento de motor de IA y las capacidades de convertidor de muestreo RF que ofrece un (1) dispositivo Versal RF VR1652 (un solo chip) frente a cuatro (4) dispositivos Virtex UltraScale+ VU13P + un (1) dispositivo de la Serie Versal AI Core VC1702 + un (1) convertidor RF AD9084 independiente ADI. Los resultados variarán según el dispositivo, el diseño, la configuración y otros factores. (VER-077)

TOPS (Tera Operations per Second, tera operaciones por segundo) para un procesador Serie AMD Versal RF es la cantidad máxima de operaciones por segundo que se pueden ejecutar en una situación óptima, que puede no ser típica. Las TOPS variarán según el dispositivo, el diseño, la configuración y otros factores. (VER-084)