Assistente de fluxo de projeto

Guia interativo para ajudar você a criar uma estratégia de desenvolvimento.

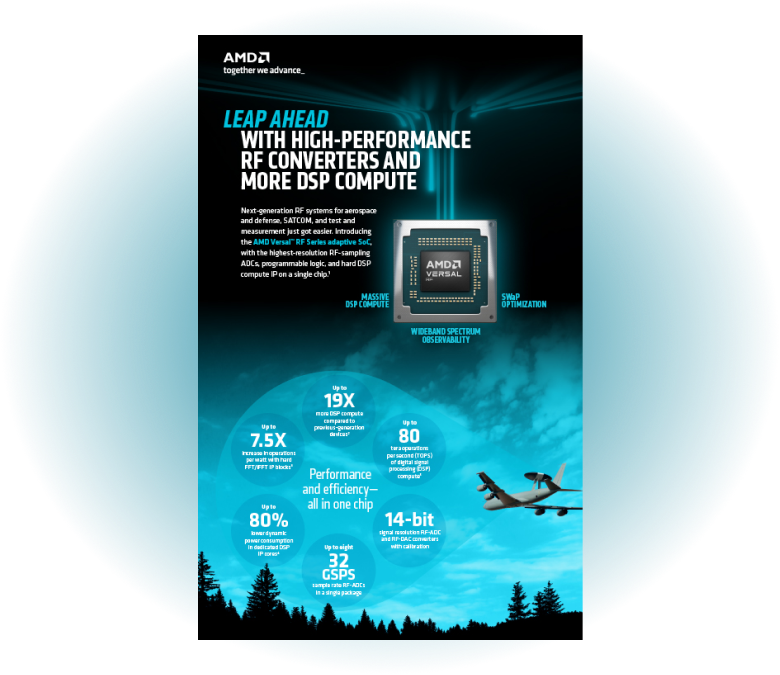

Espectro de banda larga. Computação DSP abrangente. Um único chip.

Possibilita a análise de sinal com flexibilidade, precisão e rapidez em um amplo espectro observável para aplicações de radar, análise espectral, teste e medições

Determinadas funções DSP altamente utilizadas são implementadas em blocos hard IP, reduzindo significativamente a quantidade de utilização lógica programável e o consumo de energia, e acelerando o tempo de processamento

Fornece processamento rápido de dados com tamanho, peso e potência otimizados (SWaP), o que é fundamental para aplicações avançadas de processamento de sinal

Aproveite os conversores de amostragem de RF integrados da mais alta resolução em um SoC adaptativo de chip único com lógica programável.1

O SoC adaptativo AMD Versal™ RF oferece computação de alto desempenho para as complexas cargas de trabalho de DSP dos modernos mercados aeroespacial e de defesa, e dos mercados de teste e medição avançados, em um único dispositivo que atende aos requisitos de SWaP.

Consulte a visão geral da folha de dados para saber quais são as combinações de recursos disponíveis por dispositivo/pacote.

O AMD Versal™ Série RF aproveita os benefícios da arquitetura Versal, como NoC, mecanismos de IA, lógica programável e DDR flexível, e adiciona RF-DACs e RF-ADCs de 18 GHz diretos, para obter observabilidade de espectro de banda larga e núcleos hard IP dedicados em um die monolítico, com o objetivo de atender aos rigorosos requisitos de SWaP para A&D e aplicações de teste e medição. Os blocos de hard IP incluem FFT/iFFT de 4 GSPS, canalizadores, um recoletor de amostra arbitrário polifásico e um decodificador LDPC atualizado compatível com códigos DVB-S/S2x.

Consulte a visão geral da folha de dados para saber quais são as combinações de recursos disponíveis por dispositivo/pacote.

Os dispositivos do Versa Série RF incluem RF-DACs e RF-ADCs de 14 bits, com calibração, que operam a até uma frequência de entrada e saída de 18 GHz. O RF-DAC coleta amostras a até 16 GSPS enquanto o RF-ADC aceita configurações de 8 GSPS e 32 GSPS, fornecendo um amplo espectro observável. A agilidade de frequência é fornecida por misturadores integrados de granulação grossa e fina e por meio de decimação/interpolação configuráveis. Várias combinações de RF-DACs e RF-ADCs são compatíveis, como 16 RF-DACs e 16 RF-ADCs a 8 GSPS; 8 RF-DACs e 4 RF-ADCs a 32 GSPS, e 16 RF-DACS e 8 RF-ADCs a 32 GSPS, em pacotes compatíveis, permitindo soluções dimensionáveis.

A implementação de funções altamente usadas em blocos de IP rígidos reduz a potência dinâmica em até 80% em relação a uma implementação de lógica suave da AMD2, e ocupa menos área física, o que resulta em menor tamanho geral, peso e potência (SWaP). O IP dedicado incluído no Versal Série RF é configurável para casos de uso comuns e pode reduzir profundamente a lógica programável (PL) e os mecanismos DSP necessários em um projeto típico. O Versal Série RF tem várias instâncias dos seguintes blocos de hard IP:

FFT/iFFT

Um bloco FFT/iFFT robusto e configurável a 4 GSPS de 8-pt a 4K-pt viabiliza uma rápida análise do espectro dos sinais de entrada. Se FFTs de tamanho de ponto maior forem necessários, múltiplas instâncias do bloco FFT/iFFT robusto podem ser combinadas com o PL.

Canalizador

Um banco de filtro polifásico canalizador separa o espectro de entrada de banda larga em subcanais estreitos, permitindo assim a rápida identificação e caracterização dos sinais de entrada. Múltiplas instâncias do canalizador IP podem ser sobrepostas para aumentar a resolução e a precisão da caracterização do sinal. O bloco de hard IP do canalizador também pode ser usado em reverso como um sintetizador. Além disso, o IP do canalizador pode ser usado como um filtro genérico se a função do canalizador (FFT/iFFT de 16 pontos) não for usada.

Decodificador LDPC

Uma versão atualizada do SD-FEC no Zynq™ RFSoC Gen 1 e Gen 3 está inclusa nos dispositivos Versal Série RF. Esta variante do SD-FEC aceita somente decodificação LDPC, mas adiciona os códigos de satélite DVB-S2/S2X que são compatíveis com aplicações espaciais. O uso deste bloco rígido reduz significativamente os LUTs para sistemas que usam a correção de erro de avanço LDPC, o que resulta em um consumo de energia muito menor. Nota: Os códigos turbo e a codificação LDPC não são compatíveis com o IP dedicado, embora estejam disponíveis como núcleos IP suaves.

Recoletor de amostras arbitrário e polifásico

Um bloco de hard IP de reamostragem arbitrária e polifásica (1 ≤ R≤ 2) é fornecido para aplicações de teste e medição. Este bloco de hard IP também pode ser usado para filtragem geral.

O Versal Série RF contém um processador de aplicação Arm Cortex-A72 dual-core e um processador em tempo real Arm Cortex-R5F dual-core para atender às diversas necessidades de aplicação. A unidade de processamento de aplicações é ideal para aplicações complexas compatíveis com um sistema operacional, e a unidade de processamento em tempo real é ideal para aplicações que precisam de baixa latência, determinismo e controle em tempo real. Um terceiro controlador de gerenciamento de plataforma separado gerencia a inicialização, a segurança e a depuração do sistema.

A lógica programável possibilita o desenvolvimento de blocos computacionais personalizados para algoritmos em constante mudança. Carregado com uma ampla variedade de elementos de memória fortemente acoplada à E/S programável, a lógica programável permite que os usuários criem aceleradores poderosos para qualquer aplicação.

O X5IO de alto desempenho com MIPI D-PHY de até 4,5 GB/s e o C-PHY de até 10 GB/s fornecem flexibilidade, processamento em tempo real e adaptabilidade futura.

Os mecanismos de DSP aprimorados oferecem suporte a novas operações e tipos de dados, incluindo ponto flutuante de precisão simples e de meia precisão e operações complexas de 18x18. Com a compatibilidade com versões anteriores para projetos de dispositivos AMD UltraScale+™, os usuários podem continuar aproveitando suas atuais bibliotecas e IP, ou podem atualizar seus projetos para capturar o desempenho de computação aprimorado habilitado por essa nova arquitetura.

Os SoCs adaptativos do Versal AI Engine Série RF é um mecanismo de IA de primeira geração otimizado para computação DSP em tempo real, que fornece desempenho determinista.

Os controladores de memória de hard DDR aceitam os tipos de memória DDR5-6400 e LPDDR5X-8533 com nova funcionalidade de criptografia em linha, oferecendo largura de banda de memória de até 136,5 GB/s.

Saiba como o Versal Série RF com RF-ADCs, RF-DACs e blocos de hard IP pode fornecer uma solução de chip único para o seu sistema RF com SWaP muito menor.

As Operações de Espectro Eletromagnético (Electromagnetic Spectrum Operations – EMSO) estão se tornando cada vez mais desafiadoras, à medida que o espectro se torna mais congestionado e disputado. O Versal Série RF ajuda a lidar com as capacidades de EMSO em um dispositivo monolítico altamente otimizado e com eficiência de SWaP. Com conversores de dados a 32 GSPS compatíveis com até Banda Ku e com novos blocos de hard IP, o Versal Série RF integra as capacidades de um Zynq UltraScale+ RFSoC e a alta contagem de processamento de sinal digital (DSP) do Versal Série Premium em um único dispositivo Versal Série RF.

Com computação de processamento de sinal digital (DSP) avançada e monoliticamente integrada, e com conversores de dados de 14 bits de alta resolução gerando amostras a 32 GSPS com até 18 GHz, o AMD Versal Série RF é compatível com uma ampla gama de aplicações de teste e medição em equipamento de teste automatizado (ATE) de semicondutores, no setor aeroespacial e de defesa, em instrumentos de bancada e em 6G.

| VR1602 | VR1652 | VR1902 | VR1952 | ||

| RF-ADC de 14 bits | Nº de ADCs | 16 | 4 | 16 | 8 |

| Taxa de Amostra Máxima (GSPS) | 8 | 32 | 8 | 32 | |

| RF-DAC de 14 bits | Nº de DACs | 16 | 8 | 16 | 16 |

| Taxa de Amostra Máxima (GSPS) | 16 | 16 | 16 | 16 |

| VR1602 | VR1652 | VR1902 | VR1952 | |

| Blocos do mecanismo de IA | 126 | 126 | 120 | 120 |

| Decodificador LDPC | 4 | 4 | - | - |

| Canalizador | 224 | 224 | 320 | 320 |

| FFT/iFFT | 28 | 28 | 40 | 40 |

| Recoletor de amostras arbitrário e polifásico | - | - | 8 | 8 |

| VR1602 | VR1652 | VR1902 | VR1952 | |

| Unidade de processamento de aplicações | Unidade de processamento de aplicações Arm® Cortex®-A72 dual-core, cache L1 de 48 KB/32 KB com paridade e ECC; cache L2 de 1 MB com ECC | |||

| Unidade de processamento em tempo real | Unidade de processamento em tempo real Arm Cortex-R5F de núcleo duplo, 32 KB/cache L1 de 32 KB e TCM de 256 KB com ECC | |||

| Memória | 256 KB de memória no chip com ECC | |||

| Conectividade | Conectividade Ethernet (x2); UART (x2); CAN-FD (x2); USB 2.0 (x1); SPI (x2); I2C (x2) | |||

| VR1602 | VR1652 | VR1902 | VR1952 | |

| Células lógicas do sistema | 1.205.400 | 1.205.400 | 2.473.800 | 2.473.800 |

| LUTs | 551.040 | 551.040 | 1.130.880 | 1.130.880 |

| DSP58 | 2.256 | 2.256 | 3.976 | 3.976 |

| VR1602 | VR1652 | VR1902 | VR1952 | |

| Memória PL total (Mb) | 156 | 156 | 189 | 189 |

| Controladores de memória DDR | 4 | 4 | 4 | 4 |

| Transceptores GTYP | 12 | 12 | - | - |

| Transceptores GTM (56G (112G)) | 8 (4) | 8 (4) | - | - |

| Transceptores GTMP (56 G (112 G)) | - | - | 20 (10) | 20 (10) |

| MAC multitaxa ethernet de 100 G | 2 | 2 | 2 | 2 |

| MAC Ethernet 600G | - | - | 3 | 3 |

| PL PCIe (5ª geração x4) | 1 | 1 | 1 | 1 |

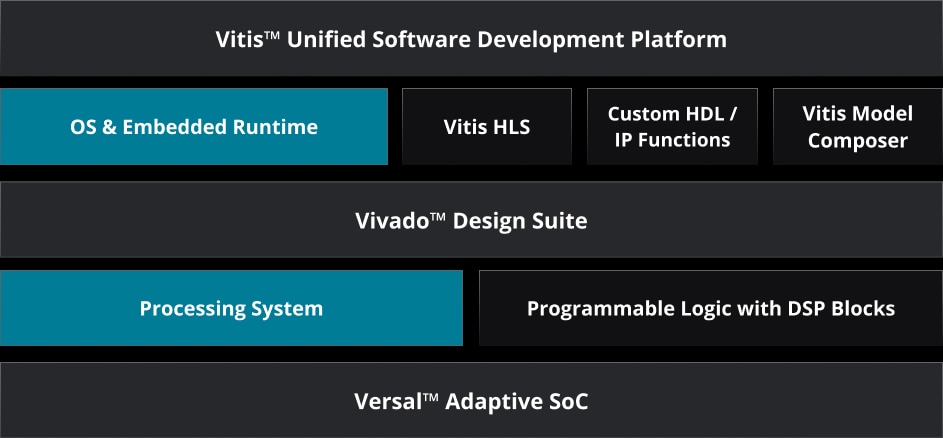

A AMD oferece um ambiente líder de desenvolvimento de software para projetar com SoCs adaptativos e FPGAs, incluindo ferramentas (compiladores, simuladores etc.), IP e soluções.

Esse ambiente pode reduzir o tempo de desenvolvimento, permitindo que os desenvolvedores alcancem alto desempenho por watt. Essas ferramentas possibilitam que todos os tipos de desenvolvedores, engenheiros de aplicações e de algoritmos, desenvolvedores de software integrado e desenvolvedores de hardware tradicionais usem soluções de computação adaptativa da AMD.

O Versal Série RF está atualmente em etapa de acesso antecipado. Converse com seu representante de vendas local da AMD para se candidatar ao Programa de acesso antecipado ou visite a página Entrar em contato com o departamento de vendas.

Junte-se à lista de notificações do SoC adaptativo do Versal para receber as últimas notícias e atualizações.

Com base na análise interna da AMD para calcular a computação DSP teórica (incluindo hard IP, mecanismos de IA e DSP) no modo canalizador oferecido pelos dispositivos Versal Série RF, em comparação com a computação DSP publicada da geração anterior do Zynq UltraScale+ RFSoC de 3ª geração, na data setembro de 2024. Os resultados reais ivariarão com base na configuração, no dispositivo, no projeto e em outros fatores. (VER-068)

Com base na projeção de engenharia da AMD de valores de energia de hard IP em novembro de 2024. O AMD Power Design Manager (2023.2.2) foi usado para determinar a energia total da lógica flexível, com base no catálogo IP do Vivado 2023.2.2. (VER-074)

Com base em uma análise interna da AMD em novembro de 2024, com o objetivo de comparar a quantidade de processamento DSP, computação do mecanismo de IA e recursos de conversor de amostragem de RF oferecidos por um dispositivo (1) Versal RF VR1652 (chip único) em relação ao que é fornecido por quatro (4) dispositivos Virtex UltraScale+ VU13P mais um (1) dispositivo Versal AI Core Série VC1702 mais um (1) conversor ADI AD9084 RF dedicado. Os resultados variam de acordo com o dispositivo, o projeto, a configuração e outros fatores. (VER-077)

Trilhões de operações por segundo (TOPS) para um processador AMD Versal Série RF é o número máximo de operações por segundo que pode ser executado em um cenário ideal e pode não ser comum. Os resultados de TOPS variam de acordo com o dispositivo, o projeto, a configuração e outros fatores. (VER-084)