Bis zu 4 GHz Frequenzbetrieb

- 8 x oder 16 x 6,554 GSPS DACs

- 8 x 4,096 GSPS oder 16 x 2,058 GSPS ADCs

Die branchenweit einzige adaptive Single-Chip-Funkplattform

Mit einer typischen Laufzeit von weit über 15 Jahren können Sie sich in puncto Lebensdauer Ihres Designs auf AMD Chips verlassen – AMD 7-Serie FPGAs und adaptive SoCs halten bis 2040 und AMD UltraScale+™ FPGAs und adaptive SoCs bis 2045.

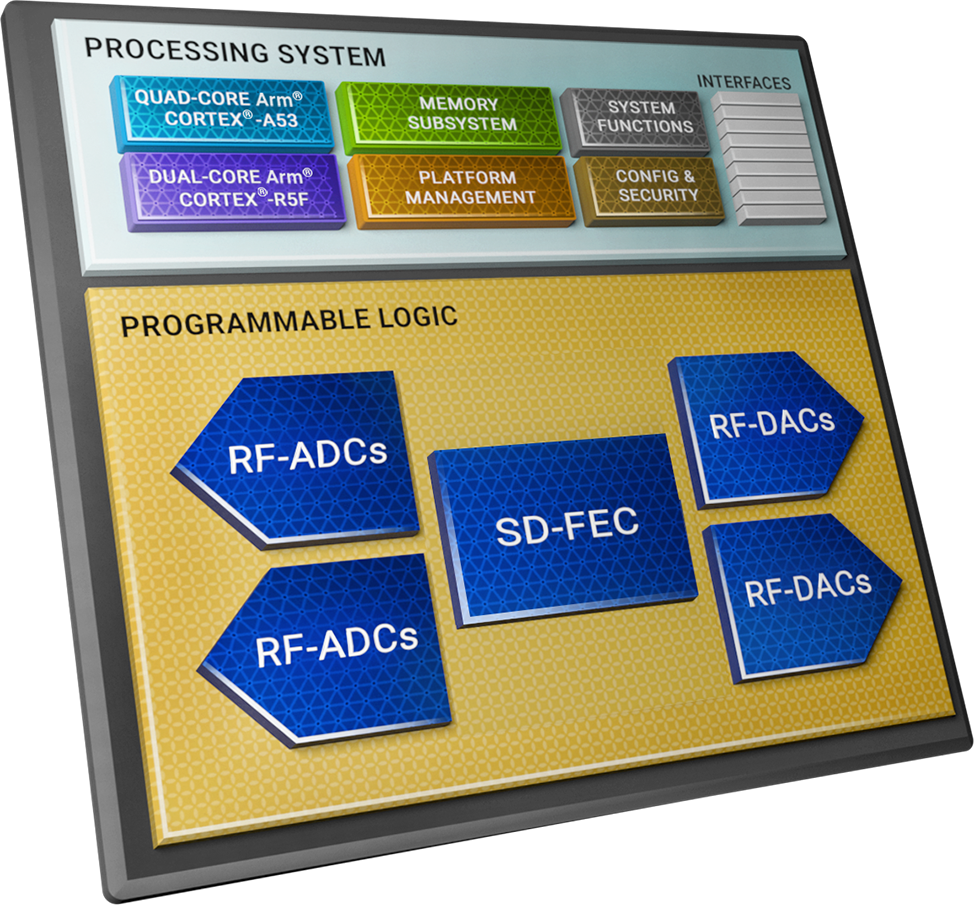

Durch die monolithische Integration von direkten RF-Sampling-Datenkonvertern in ein adaptives SoC entfällt der Bedarf an externen Datenkonvertern, wodurch eine flexible Lösung mit bis zu 50 % geringerem Energieverbrauch und geringerem Platzbedarf gegenüber einer Mehrkomponentenlösung ermöglicht wird – einschließlich der Eliminierung stromintensiver FPGA-zu-Analog-Schnittstellen wie JESD204. Dieser Ansatz ermöglicht auch eine hochflexible Lösung, bei der ein Großteil der RF-Signalverarbeitung in die digitale Domäne verschoben wird.

Das Zynq UltraScale+™ RFSoC integriert einen IP-Block mit SD-FEC-Kernen (Soft-Decision-Vorwärtsfehlerkorrektur) in LDPC (Low-Density Parity Checking) und Turbo-Codec-Unterstützung. Die gehärteten Kerne liefern eine Performance von über 1 Gb/s bei geringer Latenz sowie einen geringeren Energieverbrauch und eine kleinere Stellfläche als bei Soft-Logic-Implementierungen.

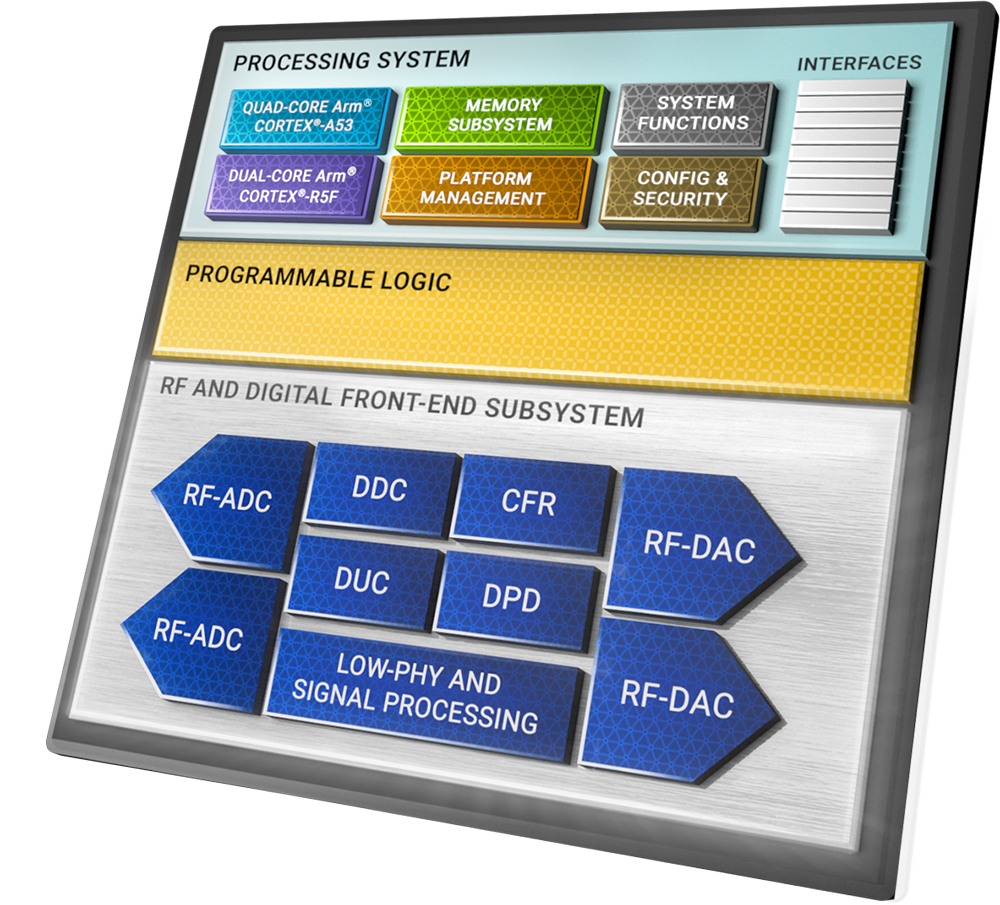

Zynq RFSoC DFE ist die neueste adaptive RFSoC Plattform, die mehr gehärtete IP als Soft Logic für kritische DFE-Verarbeitung integriert. Zynq RFSoC DFE ermöglicht eine flexible Lösung für 5G New Radio und betreibt bis zu 7,125 GHz Eingangs-/Ausgangsfrequenz mit Energie- und Kosteneffizienz.

Die Zynq UltraScale+ RFSoC Architektur integriert FPGA-Fabric für Flexibilität, um eine Vielzahl von Anforderungen mit derselben grundlegenden Hardware zu erfüllen. Die Möglichkeit, dieselbe Plattform für unterschiedliche Anforderungen und neue Standards zu nutzen, ermöglicht es Anbietern, schnell auf neue Marktchancen zu reagieren.

Als heterogene Computing-Architektur, die ein vollständiges Arm-Verarbeitungssubsystem, ein FPGA Fabric und eine vollständige analoge/digitale Programmierbarkeit über die gesamte RF-Signalkette umfasst, bieten Zynq UltraScale+ RFSoCs eine komplette, softwaredefinierte Single-Chip-Funkplattform für verschiedene Anwendungen und die Möglichkeit, Funkvarianten bei sich entwickelnder Marktdynamik zu produzieren.

Skalierbarkeit im gesamten Portfolio, das aktuellen und zukünftigen Marktanforderungen entspricht

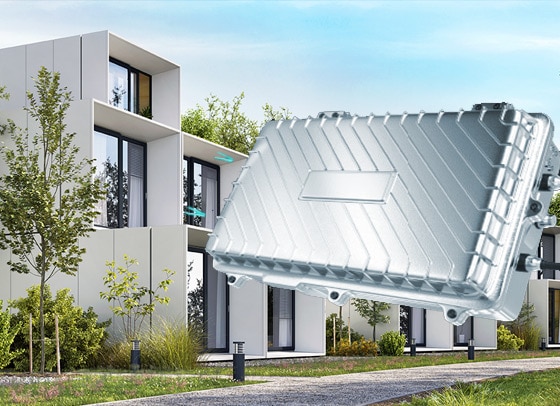

Mit Zynq RFSoC können Hersteller von drahtlosen Infrastrukturen bisher unerreichbare Stellfläche und Stromeinsparungen erzielen, was für eine massive MIMO-Bereitstellung entscheidend ist.

Zynq UltraScale+ RFSoC ermöglicht es MSOs (Multi-Service Operators), die PHY-Layer-Verarbeitung mit Remote-PHY-Knoten näher an das Zuhause zu verlagern und so die Netzwerkkapazität zu erhöhen.

Als eine Single-Chip-TRX-Lösung für skalierbaren, multifunktionalen Phased-Array-Radar sorgt das Zynq UltraScale+ RFSoC für niedrige Latenz beim Senden und Empfangen für eine optimale Reaktionszeit in Frühwarnszenarien.

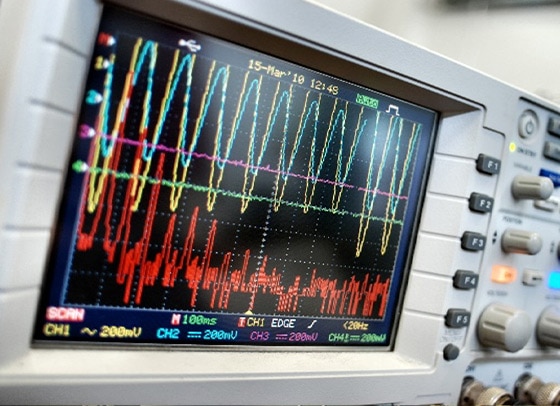

Designer können Multifunktionsgeräte mit hoher Geschwindigkeit für die Signalerzeugung und -analyse erstellen, indem sie direkte RF-Abtastung, hochflexible, rekonfigurierbare Logik und Softwareprogrammierbarkeit in Zynq UltraScale+ RFSoC verwenden.

Designer können Multifunktionsgeräte mit hoher Geschwindigkeit für die Signalerzeugung und -analyse erstellen, indem sie direkte RF-Abtastung, hochflexible, rekonfigurierbare Logik und Softwareprogrammierbarkeit in Zynq UltraScale+ RFSoC verwenden.

| ZU21DR | ZU25DR | ZU27DR | ZU28DR | ZU29DR | ||

|---|---|---|---|---|---|---|

| Max. RF-Eingangsfrequenz (GHz) | 4 | |||||

| Dezimierung/Interpolation | 1x, 2x, 4x, 8x | |||||

| 12-Bit RF-ADC | Anzahl der ADCs | – | 8 | 8 | 8 | 16 |

| Max. Rate (GSPS) | – | 4,096 | 4,096 | 4,096 | 2,058 | |

| 14-Bit RF-DAC | Anzahl der DACs | – | 8 | 8 | 8 | 16 |

| Max. Rate (GSPS) | – | 6,554 | 6,554 | 6,554 | 6,554 | |

| SD-FEC | 8 | 0 | 0 | 8 | 0 | |

| ZU21DR | ZU25DR | ZU27DR | ZU28DR | ZU29DR | |

|---|---|---|---|---|---|

| Systemlogikzellen (in Tausend) | 930 | 678 | 930 | 930 | 930 |

| DSP-Schichten | 4.272 | 3.145 | 4.272 | 4.272 | 4.272 |

| Speicher (Mb) | 60,5 | 41,3 | 60,5 | 60,5 | 60,5 |

| GTY-Transceiver | 16 | 8 | 16 | 16 | 16 |

| PCIe Gen3x16 | 2 | 1 | 2 | 2 | 2 |

| PCIe Gen3x16/ Gen4x8/CCIX | – | – | – | – | – |

| 100G Ethernet MAC/PCS mit RS-FEC | 2 | 1 | 2 | 2 | 2 |

| Maximale E/A-Pins | 280 | 347 | 347 | 347 | 408 |

| ZU21DR | ZU25DR | ZU27DR | ZU28DR | ZU29DR | |

|---|---|---|---|---|---|

| Anwendungsverarbeitungseinheit | Quad-Core Arm® Cortex®-A53 MPCore bis zu 1,33 GHz | ||||

| Echtzeitverarbeitungseinheit | Dual-Core Arm Cortex-R5 MPCore bis zu 533 MHz | ||||

| Integrierter und externer Speicher | 256 KB On-Chip-Memory mit ECC; externer DDR4; DDR3; DDR3L; LPDDR4; LPDDR3; externes Quad-SPI; NAND; eMMC | ||||

| Hochgeschwindigkeitskonnektivität | 4 PS-GTR; PCIe Gen1/2; Serial ATA 3.1; DisplayPort™ 1.2a; USB 3.0; SGMII | ||||

| Allgemeine Konnektivität | 214 PS E/A; UART; CAN; USB 2.0; I2C; SPI; 32b GPIO; Echtzeituhr; Watchdog-Timer; dreifache Timer-Zähler | ||||

| ZU39DR | ||

|---|---|---|

| Max. RF-Eingangsfrequenz (GHz) | 5 | |

| Dezimierung/Interpolation | 1x, 2x, 4x, 8x | |

| 12-Bit RF-ADC | Anzahl der ADCs | 16 |

| Max. Rate (GSPS) | 2,220 | |

| 14-Bit RF-DAC | Anzahl der DACs | 16 |

| Max. Rate (GSPS) | 6,554 | |

| SD-FEC | 0 | |

| ZU39DR | |

|---|---|

| Systemlogikzellen (K) | 930 |

| DSP-Schichten | 4.272 |

| Speicher (Mb) | 60,5 |

| GTY-Transceiver | 16 |

| PCIe Gen3x16 | 2 |

| PCIe Gen3x16/ Gen4x8/CCIX | – |

| 100G Ethernet MAC/PCS mit RS-FEC | 2 |

| Maximale E/A-Pins | 408 |

| ZU39DR | |

|---|---|

| Anwendungsverarbeitungseinheit | Quad-Core Arm Cortex-A53 MPCore bis zu 1,33 GHz |

| Echtzeitverarbeitungseinheit | Dual-Core Arm Cortex-R5 MPCore bis zu 533 MHz |

| Integrierter und externer Speicher | 256 KB On-Chip-Memory mit ECC; externer DDR4; DDR3; DDR3L; LPDDR4; LPDDR3; externes Quad-SPI; NAND; eMMC |

| Hochgeschwindigkeitskonnektivität | 4 PS-GTR; PCIe Gen1/2; Serial ATA 3.1; DisplayPort 1.2a; USB 3.0; SGMII |

| Allgemeine Konnektivität | 214 PS E/A; UART; CAN; USB 2.0; I2C; SPI; 32b GPIO; Echtzeituhr; Watchdog-Timer; dreifache Timer-Zähler |

| ZU42DR | ZU43DR | ZU46DR | ZU47DR | ZU48DR | ZU49DR | ||||

|---|---|---|---|---|---|---|---|---|---|

| Max. RF-Eingangsfrequenz (GHz) | 6 | ||||||||

| Dezimierung/Interpolation | 1 x, 2 x, 3 x, 4 x, 5 x, 6 x, 8 x, 10 x, 12 x, 16 x, 20 x, 24 x, 40 x | ||||||||

| 14-Bit RF-ADC | Anzahl der ADCs | 8 | 2 | 4 | 8 | 4 | 8 | 8 | 16 |

| Max. Rate (GSPS) | 2,5 |

5,0 |

5,0 | 2,5 | 5,0 | 5,0 | 5,0 | 2,5 | |

| 14-Bit RF-DAC | Anzahl der DACs | 8 |

4 | 12 | 8 | 8 | 16 | ||

| Max. Rate (GSPS) | 9,85* | 9,85* | 9,85* | 9,85* | 9,85* | 9,85* | |||

| SD-FEC | 0 | 0 | 8 | 0 | 8 | 0 | |||

* Wenden Sie sich an Ihren lokalen AMD Vertriebsmitarbeiter, um Support für 10-GSPS-Geräte zu erhalten

| ZU42DR | ZU43DR | ZU46DR | ZU47DR | ZU48DR | ZU49DR | |

|---|---|---|---|---|---|---|

| Systemlogikzellen (K) | 489 | 930 | 930 | 930 | 930 | 930 |

| DSP-Schichten | 1.872 | 4.272 | 4.272 | 4.272 | 4.272 | 4.272 |

| Speicher (Mb) | 67,8 | 60,5 | 60,5 | 60,5 | 60,5 | 60,5 |

| GTY-Transceiver | 8 | 16 | 16 | 16 | 16 | 16 |

| PCIe Gen3x16 | – | – | – | – | – | – |

| PCIe Gen3x16/ Gen4x8/CCIX | 0 | 2 | 2 | 2 | 2 | 2 |

| 100G Ethernet MAC/PCS mit RS-FEC | 0 | 2 | 2 | 2 | 2 | 2 |

| Maximale E/A-Pins | 152 | 347 | 360 | 347 | 347 | 408 |

| ZU42DR | ZU43DR | ZU46DR | ZU47DR | ZU48DR | ZU49DR | |

|---|---|---|---|---|---|---|

| Anwendungsverarbeitungseinheit | Quad-Core Arm Cortex-A53 MPCore bis zu 1,33 GHz | |||||

| Echtzeitverarbeitungseinheit | Dual-Core Arm Cortex-R5F MPCore bis zu 533 MHz | |||||

| Integrierter und externer Speicher |

256 KB On-Chip-Memory mit ECC; externer DDR4; DDR3; DDR3L; LPDDR4; LPDDR3; externes Quad-SPI; NAND; eMMC |

|||||

| Hochgeschwindigkeitskonnektivität | 4 PS-GTR; PCIe Gen1/2; Serial ATA 3.1; DisplayPort™ 1.2a; USB 3.0; SGMII | |||||

| Allgemeine Konnektivität | 214 PS E/A; UART; CAN; USB 2.0; I2C; SPI; 32b GPIO; Echtzeituhr; Watchdog-Timer; dreifache Timer-Zähler | |||||

| ZU63DR | ZU64DR | ZU65DR | ZU67DR |

|||||

|---|---|---|---|---|---|---|---|---|

| Max. RF-Eingangsfrequenz (GHz) | 7,125 | |||||||

| Dezimierung/Interpolation | 1 x, 2 x, 3 x, 4 x, 5 x, 6 x, 8 x, 10 x, 12 x, 16 x, 20 x, 24 x, 40 x | |||||||

| 14-Bit RF-ADC | Anzahl der ADCs | 4 | 2 | 8 | 2 | 6 | 8 | 2 |

| Max. Rate (GSPS) | 2,95 | 5,9 | 2,95 | 5,9 | 5,9 |

2,95 | 5,9 | |

| 14-Bit RF-DAC | Anzahl der DACs | 4 | 8 | 6 |

8 | |||

| Max. Rate (GSPS) | 10,0* | 10,0* | 10,0* | 10,0* | ||||

| Digital Front-End (DFE) Hard IP | Kanalfilter, DUC/DDC, Mischer, CFR, komplexer Equalizer, PQ, Resampler, DPD | |||||||

| Low PHY Hard IP | FFT/IFFT, PRACH | – | FFT/IFFT, PRACH | FFT/IFFT, PRACH | ||||

| SD-FEC | 0 | 0 | 0 | 0 | ||||

* Wenden Sie sich an Ihren lokalen AMD Vertriebsmitarbeiter, um Support für 10-GSPS-Geräte zu erhalten

| ZU63DR | ZU64DR | ZU65DR | ZU67DR | |

|---|---|---|---|---|

| Systemlogikzellen (in Tausend) | 393 | 328 | 489 | 489 |

| DSP-Schichten | 1.200 | 1.872 | 1.872 | 1.872 |

| Speicher (Mb) | 54,2 | 38,3 | 67,8 | 67,8 |

| GTY-Transceiver | 4 | 8 | 8 | 8 |

| PCIe Gen3x16 | 0 | 0 | 0 | 0 |

| PCIe Gen3x16/ Gen4x8/CCIX | 0 | 0 | 0 | 0 |

| 100G Ethernet MAC/PCS mit RS-FEC | 1 | 1 | 1 | 1 |

| Maximale E/A-Pins | 154 | 154 | 154 | 154 |

| ZU63DR | ZU64DR | ZU65DR | ZU67DR | |

|---|---|---|---|---|

| Anwendungsverarbeitungseinheit | Quad-Core Arm® Cortex®-A53 MPCore™ bis zu 1,33 GHz | |||

| Echtzeitverarbeitungseinheit | Dual-Core Arm Cortex-R5F MPCore bis zu 533 MHz | |||

| Integrierter und externer Speicher |

256 KB On-Chip-Memory mit ECC; externer DDR4; DDR3; DDR3L; LPDDR4; LPDDR3; externes Quad-SPI; NAND; eMMC | |||

| Hochgeschwindigkeitskonnektivität | 4 PS-GTR; PCIe Gen1/2; Serial ATA 3.1; DisplayPort™ 1.2a; USB 3.0; SGMII | |||

| Allgemeine Konnektivität | 214 PS E/A; UART; CAN; USB 2.0; I2C; SPI; 32b GPIO; Echtzeituhr; Watchdog-Timer; dreifache Timer-Zähler | |||

Starten Sie direkt Ihren Designzyklus und erzielen Sie eine schnelle Markteinführung mit bewährter Hardware, Software-Support, Tools, Konzeptbeispielen und für das Kit verfügbarer Dokumentation.

Das Zynq UltraScale+ RFSoC DFE ZCU670 Evaluierungskit ist die optimale Plattform für die adaptive Funkentwicklung und Out-of-Box-Evaluierung bei der schnellen Prototypenerstellung von 5G New Radio (5G NR), Radar und einer Vielzahl von RF-Anwendungen.

Vereinfacht das Systemdesign mit weniger Komponenten und bietet Flexibilität bei der Plattformhardware und -software.

Für Entwickler stehen eine Vielzahl von Lösungen zur Verfügung, mit denen sie Designs auf Zynq UltraScale+ RFSoCs einfach evaluieren und debuggen können. Diese Lösungen bestehen aus Tools, IP- und Referenzdesigns, die eine breite Palette von Funktionen ermöglichen, von der Performance-Bewertung bis zum Debugging auf Systemebene, während das Benutzerdesign in der Hardware ausgeführt wird.

Diese Tools dienen als Plattform zur effektiven Konfiguration und Überwachung der Zynq UltraScale+ RFSoC Funktionen und zur Beschleunigung der Produktdesignzyklen.

Das Evaluierungstool besteht aus einem Referenzdesign für die Zynq UltraScale+ RFSoC ZCU111 Evaluierungsplatine mit einer benutzerdefinierten Benutzeroberfläche zur Konfiguration des Betriebs der RF-Datenkonverter und zur Evaluierung der Performance der RF-ADCs und RF-DACs.

Evaluierungstool-Benutzerhandbücher

Downloads für Evaluierungstool

Das Evaluierungstool besteht aus einem Referenzdesign für die Evaluierungsplatinen Zynq UltraScale+ RFSoC ZCU208 und ZCU216 mit einer benutzerdefinierten Benutzeroberfläche zur Konfiguration des Betriebs der RF-Datenkonverter und zur Evaluierung der Performance der RF-ADCs und RF-DACs.

Evaluierungstool-Benutzerhandbücher

Das Tool „RF Analyzer“ bietet eine einfache Möglichkeit, RF-Datenkonverter in Zynq UltraScale+ RFSoC Geräten auf jeder Benutzerplatine zu konfigurieren und zu debuggen. Dieses Tool ermöglicht Debugging-Funktionen über eine einfache grafische Benutzeroberfläche und interagiert nahtlos mit dem IP-Beispieldesign des RF-Datenkonverters, das auf der Benutzerplatine implementiert ist.

Das Tool „RF Analyzer“ wird nur in der Windows-Umgebung unterstützt.

Benutzerhandbücher

Der Frequenzplaner unterstützt die Frequenzplanung für Zynq UltraScale+ RFSoC Geräte.

Kurzanleitung

RFSoC Frequenzplaner – Downloads

Vivado™ Projekte ermöglichen Entwicklern, End-to-End-Designs mit Zynq UltraScale+ RFSoCs zu starten.

Designdokumente

Designdateien – Downloads

Mit dem ZCU111 Evaluierungskit implementiert diese Demo eine drahtlose Lösung unter Verwendung von PYNQ- und Jupyter-Notebooks.

Unser Vertriebsteam unterstützt Sie bei der Auswahl der besten Technologien für Ihre spezifischen Anforderungen.