Téléchargements

Rendez-vous sur la page de téléchargement pour accéder à notre nouvelle plateforme software unifiée AMD Vitis™.

Version 2024.2 désormais disponible

La plateforme software AMD Vitis™ est un environnement de développement de conceptions comprenant une structure FPGA, des sous-systèmes de processeur Arm® et des moteurs d'IA. Les outils Vitis fonctionnent en conjonction avec AMD Vivado™ Design pour fournir un plus haut niveau d'abstraction pour le développement de conceptions.

Vitis™ Embedded est un package de développement software intégré autonome, destiné au développement d'applications hôtes s'exécutant sur des processeurs Arm intégrés.

Les SoC adaptatifs AMD Versal™ utilisent des matrices AI Engine qui permettent d’implémenter des fonctions DSP à hautes performances en gérant les ressources et l’énergie de manière optimale. L'utilisation de moteurs d'IA en conjonction avec les ressources de la structure FPGA permet d'implémenter des applications DSP hautes performances de façon très efficace.

L'outil Vitis HLS permet aux utilisateurs de créer facilement des algorithmes FPGA complexes en synthétisant une fonction C/C++ dans le RTL.

L'outil Vitis HLS est étroitement intégré à Vivado™ Design pour la synthèse, le placement et le routage, ainsi qu'à la plateforme software unifiée Vitis pour les conceptions et applications de systèmes hétérogènes.

Vitis Model Composer est un outil de conception basé sur un modèle qui permet une exploration rapide des conceptions dans l'environnement MathWorks Simulink®.

Cet outil vous permet également de modéliser et de simuler des conceptions avec des moteurs d'IA et des blocs de logique programmable (HDL/HLS).

Des bibliothèques open source pour des performances optimisées, accélérant directement vos applications existantes codées en C ou C++, et ne nécessitant presque aucune modification du code.

Tirez directement parti des bibliothèques accélérées pour chaque domaine, modifiez-les en fonction de vos exigences ou utilisez-les comme des blocs de construction algorithmiques dans vos accélérateurs personnalisés.

Plusieurs outils Vitis doivent être utilisés pour créer les différentes parties des FPGA et SoC adaptatifs AMD.

| FPGA (logique programmable) | Sous-système de traitement | Moteurs d'IA |

|---|---|---|

| Suite Vivado Design/Vitis HLS/Vitis Model Composer | Vitis Embedded | Compilateurs et simulateurs AIE/Vitis Model Composer |

(généralement appelé SDK intégré pour les familles FPGA précédentes)

Export du hardware de Vivado en tant que fichier de plateforme |

Développement du code de l'application

|

Débogage et génération d'images de démarrage |

Les concepteurs qui codent en C/C++ pour le sous-système de processeur intégré Arm® dans les SoC adaptatifs AMD utiliseront généralement ce flux.

Les développeurs peuvent effectuer toutes les vérifications au niveau du système dans le software Vitis Embedded et générer des images de démarrage pour lancer l'application.

Pour en savoir plus sur le flux de développement d'applications software intégrées via la plateforme Vitis, reportez-vous à la section Outils Vitis pour le développement de software intégrés du Guide de l'utilisateur (UG1400).

(hardware et software)

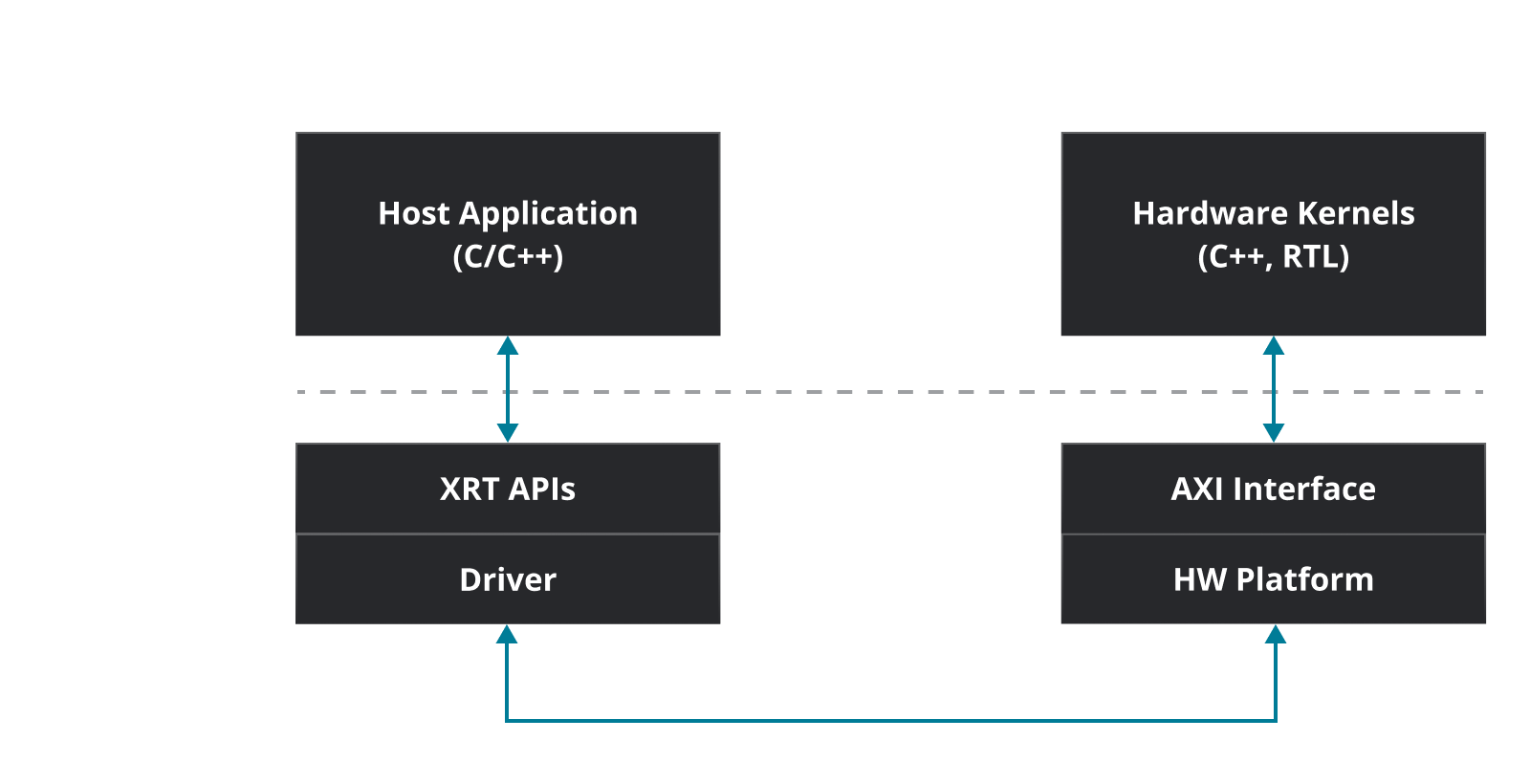

Les concepteurs de systèmes qui intègrent à la fois les parties software et hardware de leurs conceptions dans les SoC adaptatifs AMD utiliseront généralement ce flux.

Ce flux permet de développer des conceptions de systèmes intégrés hétérogènes, notamment des applications software exécutées sur des processeurs intégrés Arm® et des noyaux de calcul s'exécutant sur des matrices à logique programmable (PL) et/ou sur des matrices AI Engine Versal™.

Ce flux comprend :

Pour en savoir plus sur le flux de conception de systèmes hétérogènes à l'aide de la plateforme software unifiée Vitis, reportez-vous à la section Outils Vitis pour la conception de systèmes hétérogènes du Guide de l'utilisateur (UG1393).

Les cartes d'accélération pour centres de données AMD Alveo™ utilisent ce même flux de conception de systèmes : le programme software s'exécute sur un hôte x86 et les noyaux s'exécutent dans le FPGA sur une carte d'accélération PCIe®. Pour en savoir plus sur le flux d'accélération pour les centres de données via la plateforme software unifiée Vitis, reportez-vous à la section Outils Vitis d'accélération pour les centres de données du Guide de l'utilisateur (UG1393).

Pour plus d'informations, consultez nos pages relatives aux nouveautés ainsi qu'à l'intégrité et au cryptage des données AMD Vitis.