Descargas

Visita la página de descarga para acceder a la nueva plataforma de software unificada AMD Vitis™.

Versión 2024.2 disponible ahora

La plataforma de software AMD Vitis™ es un entorno de desarrollo para elaborar diseños que incluyen la estructura de FPGA (Field-Programmable Gate Arrays, matriz de puertas lógicas programable en campo), subsistemas de procesador Arm® y motores de IA. Las herramientas de Vitis funcionan en conjunto con AMD Vivado™ Design Suite a fin de proporcionar un nivel más alto de abstracción para el desarrollo del diseño.

Vitis™ Embedded es un paquete de desarrollo de software integrado independiente que permite desarrollar aplicaciones host que se ejecutan en procesadores integrados Arm.

Los dispositivos SoC adaptables AMD Versal™ cuentan con matrices de motor de IA que permiten la implementación de funciones de DSP de alto rendimiento de una manera optimizada en términos de recursos y energía. El uso de motores de IA junto con los recursos de la estructura de FPGA puede permitir una implementación muy eficiente de aplicaciones de DSP de alto rendimiento.

La herramienta de HLS (high-level synthesis, síntesis de alto nivel) de Vitis permite a los usuarios crear con facilidad algoritmos de FPGA complejos sintetizando una función C/C++ en el RTL (register-transfer level, nivel de transferencia de registros).

La herramienta de HLS de Vitis está estrechamente integrada tanto en Vivado™ Design Suite para la síntesis, la ubicación, la ruta, como en la plataforma de software unificada Vitis, para diseños y aplicaciones de sistemas heterogéneos.

Vitis Model Composer es una herramienta de diseño basada en el modelo que permite una exploración rápida del diseño dentro del entorno de MathWorks Simulink®.

La herramienta también te permite modelar y simular un diseño con una combinación de motor de IA y bloques de lógica programable (HDL/HLS).

Bibliotecas de código abierto y rendimiento optimizado que ofrecen aceleración lista para usar con cambios de código mínimos o nulos en sus aplicaciones existentes, escritas en C, C++.

Aprovecha las bibliotecas aceleradas específicas del dominio tal como están, modifícalas para adaptarlas a tus requisitos o utilízalas como bloques de creación algorítmicos en tus aceleradores personalizados.

Se deben utilizar diferentes herramientas de Vitis para construir diferentes partes de SoC adaptables y FPGA de AMD.

| FPGA (lógica programable) | Subsistema de procesamiento | Motores AI |

|---|---|---|

| Vivado Design Suite/Vitis HLS/Vitis Model Composer | Vitis Embedded | Compiladores y simuladores de AIE/Vitis Model Composer |

(Tradicionalmente llamado SDK integrado para familias de FPGA anteriores)

Exporta el hardware desde Vivado como un archivo de plataforma |

Desarrolla el código de aplicación

|

Depura y genera imagen de arranque |

Los diseñadores que desarrollan código C/C++ para el subsistema de procesador integrado Arm® en SoC adaptables de AMD normalmente utilizarán este flujo.

Los desarrolladores pueden realizar toda la verificación a nivel del sistema dentro del software Vitis Embedded y generar imágenes de arranque para iniciar la aplicación.

Para obtener más información sobre el flujo de trabajo de desarrollo de aplicaciones de software integrado mediante la plataforma de software Vitis, consulte la sección Herramientas de Vitis para el desarrollo de software integrado en la Guía del usuario (UG1400).

(Hardware y software)

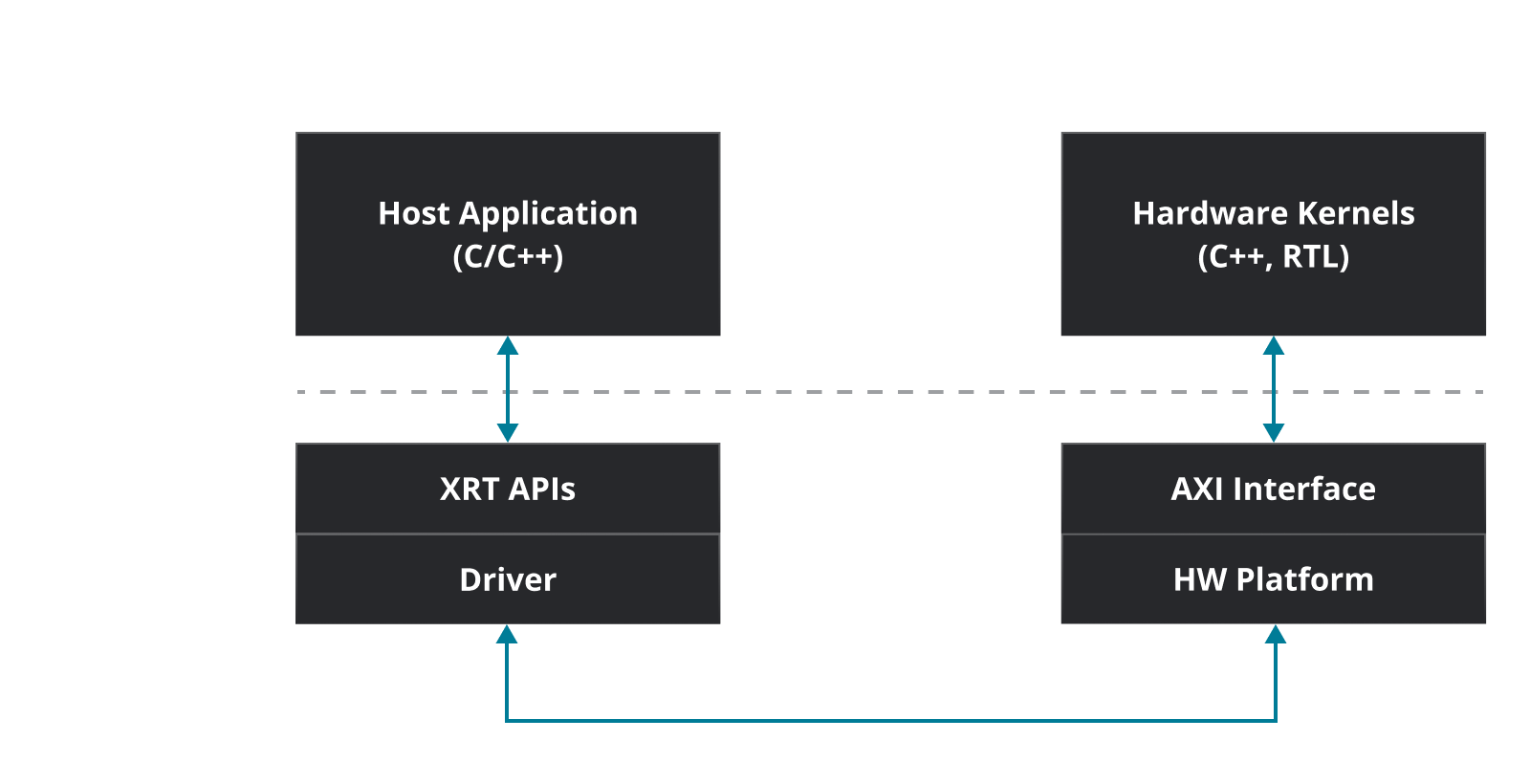

Los diseñadores de sistemas que integran las partes de software y hardware de su diseño en SoC adaptables de AMD normalmente utilizarán este flujo.

Este flujo se utiliza para desarrollar diseños de sistemas integrados heterogéneos que comprenden aplicaciones de software que se ejecutan en procesadores integrados Arm® y núcleos de procesamiento que se ejecutan en PL (programmable logic, lógica programable) o matrices de motores de IA de Versal™.

Este flujo comprende:

Para obtener más información sobre el flujo de diseño de sistemas heterogéneos mediante la plataforma de software unificada Vitis, consulta la sección Herramientas de Vitis para el diseño de sistemas heterogéneos en la Guía del usuario (UG1393).

Las tarjetas aceleradoras del centro de datos AMD Alveo™ emplean el mismo flujo de diseño de sistema: el programa de software se ejecuta en un host x86 y los núcleos se ejecutan en la FPGA en una tarjeta de aceleración conectada a PCIe®. Para obtener más información sobre el flujo de aceleración del centro de datos mediante la plataforma de software unificada Vitis, consulta la sección Herramientas de Vitis para la aceleración del centro de datos en la Guía del usuario (UG1393).

Para obtener más detalles, visita nuestras páginas Novedades y AMD Vitis IDE.