Downloads

Besuchen Sie die Download-Seite, um auf die neue AMD Vitis™ Unified Software Platform zuzugreifen.

Release 2024.2 jetzt verfügbar

Die Softwareplattform AMD Vitis™ ist eine Umgebung zur Entwicklung von Konzepten, die FPGA-Strukturen, Arm® Prozessor-Subsysteme und KI-Engines umfasst. Die Vitis Tools bieten in Verbindung mit der AMD Vivado™ Design Suite eine höhere Abstraktionsebene zur Ausarbeitung des Konzepts.

Vitis™ Embedded ist ein eigenständiges integriertes Softwareentwicklungspaket zur Entwicklung von Host-Anwendungen, die auf integrierten Arm Prozessoren ausgeführt werden.

Adaptive Versal™ SoC Geräte von AMD haben KI-Engine-Arrays, die die Implementierung von DSP-High-Performance-Funktionen in einer ressourcen- und leistungsoptimierten Art und Weise ermöglichen. Die Nutzung von KI-Engines in Verbindung mit den FPGA-Strukturressourcen können eine äußerst effiziente Implementierung von DSP-High-Performance-Anwendungen ermöglichen.

Das Vitis HLS Tool ermöglicht es, durch Synthetisieren einer C/C++-Funktion in der RTL komplexe FPGA-Algorithmen zu generieren.

Das Vitis HLS Tool bietet eine enge Integration mit der Vivado™ Design Suite, sodass Synthese- und Place-and-Route-Funktionen genutzt werden können, und mit der Vitis Unified Software Platform, auf der heterogene Systemkonzepte und Anwendungen entwickelt werden.

Vitis Model Composer ist ein modellbasiertes Designtool, das eine rasche Konzeptuntersuchung in der MathWorks Simulink® Umgebung ermöglicht.

Mithilfe des Tools können Sie außerdem ein Konzept mit einer Mischung aus KI-Engine und Blöcken mit programmierbarer Logik (HDL/HLS) modellieren und simulieren.

Für Performance optimierte Open-Source-Bibliotheken, die sofortige Beschleunigung mit minimalen bis gar keinen Codeänderungen an bestehenden Anwendungen, die in C/C++ geschrieben sind, bieten.

Nutzen Sie die domänenspezifischen beschleunigten Bibliotheken unverändert, ändern Sie diese entsprechend Ihren Anforderungen oder verwenden Sie sie als Algorithmusbausteine in Ihren benutzerdefinierten Beschleunigern.

Unterschiedliche Vitis Tools müssen eingesetzt werden, um verschiedene Teile der adaptiven SoCs und FPGAs von AMD aufzubauen.

| FPGA (programmierbare Logik) | Verarbeitungssubsystem | KI-Engines |

|---|---|---|

| Vivado Design Suite / Vitis HLS / Vitis Model Composer | Vitis Embedded | AIE-Compiler und -Simulatoren / Vitis Model Composer |

(Traditionell bezeichnet als Embedded SDK bei vorherigen FPGA Familien)

Hardware aus Vivado-as-a-Platform-Datei exportieren |

Anwendungscode entwickeln

|

Debuggen und Boot-Image generieren |

Designer, die C/C++-Code für das integrierte Arm® Prozessor-Subsystem in adaptiven SoCs von AMD entwickeln, verwenden in der Regel diesen Flow.

Entwickler können die gesamte Verifizierung auf Systemebene innerhalb der Vitis Embedded Software durchführen und Boot-Images zum Start der Anwendung generieren.

Weitere Informationen über den Entwicklungs-Workflow der integrierten Softwareanwendung mithilfe der Vitis Softwareplattform finden Sie im User Guide im Abschnitt zu Vitis Tools für die Entwicklung von Embedded Software (UG1400).

(Hardware und Software)

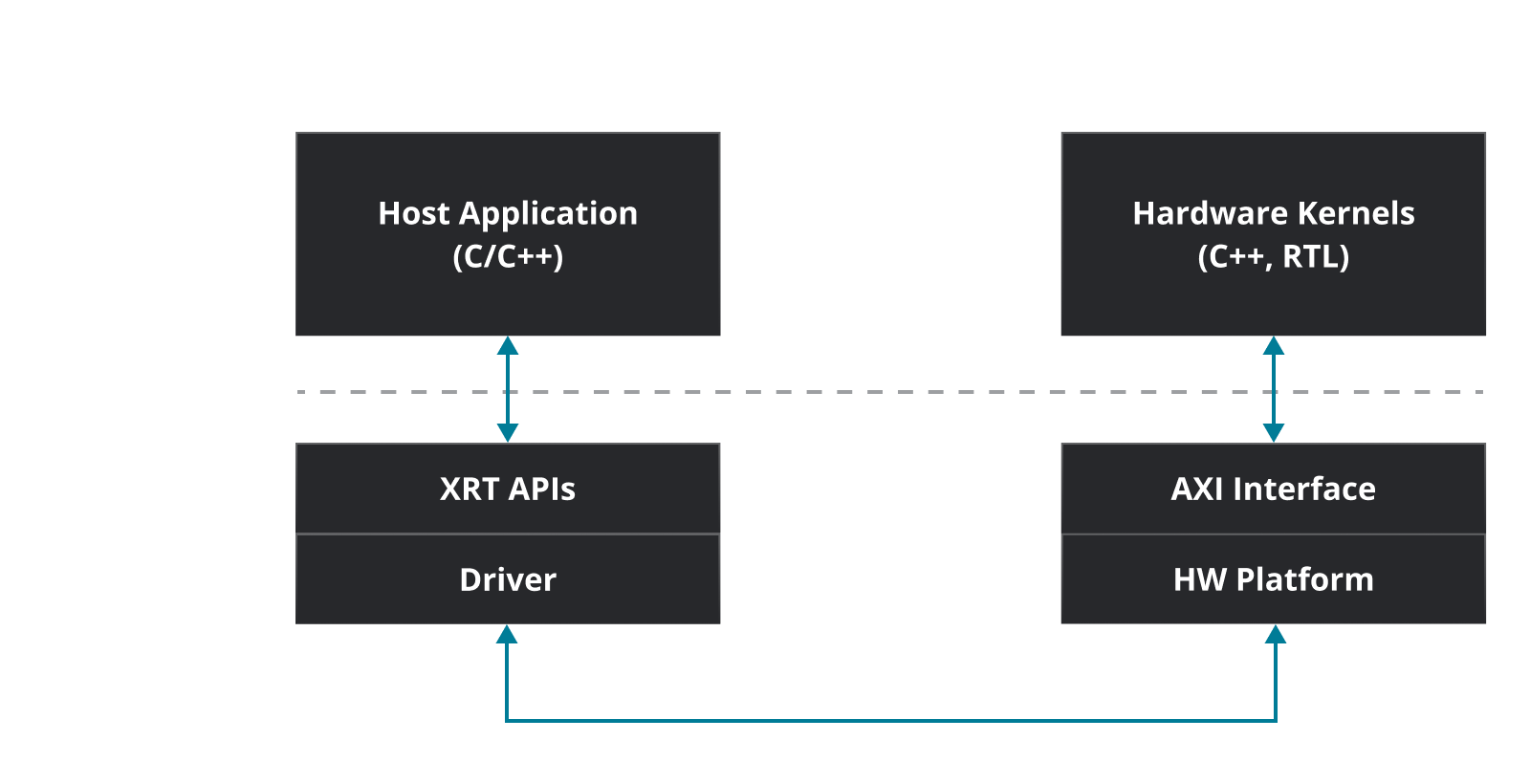

Systementwickler, die sowohl die Software- als auch die Hardwarebestandteile ihres Designs in adaptive SoCs von AMD integrieren, verwenden in der Regel diesen Flow.

Dieser Flow wird verwendet, um heterogene integrierte Systemdesigns zu entwickeln, die aus Softwareanwendungen mit integrierten Arm® Prozessoren und Computing-Kernels bestehen, die auf programmierbarer Logik (PL) und/oder Versal™ AI Engine Arrays ausgeführt werden.

Dieser Flow umfasst:

Weitere Informationen über den heterogenen Systemdesign-Flow mithilfe der Vitis Unified Software Platform finden Sie im User Guide im Abschnitt zu Vitis Tools für das heterogene Systemdesign (UG1393).

AMD Alveo™ Beschleunigerkarten für Rechenzentren nutzen denselben Systemdesign-Flow – das Softwareprogramm wird auf einem x86-Host und die Kernels auf dem FPGA auf einer PCIe®-gebundenen Beschleunigerkarte ausgeführt. Weitere Informationen über den Rechenzentrumsbeschleunigungs-Flow mithilfe der Vitis Unified Software Platform finden Sie im User Guide im Abschnitt zu Vitis Tools für die Beschleunigung im Rechenzentrum (UG1393).

Weitere Informationen erhalten Sie auf den Seiten für „Neues“ und „AMD Vitis IDE“.