Vitis 소프트웨어 플랫폼 개발 환경

AMD Vitis™ 소프트웨어 플랫폼은 FPGA 패브릭, Arm® 프로세서 하위 시스템, AI 엔진이 포함된 설계를 개발할 수 있는 개발 환경입니다. Vitis 도구는 AMD Vivado™ Design Suite와 함께 작동하여 설계 개발 시 높은 수준의 추상화를 제공합니다.

Vitis 소프트웨어 플랫폼에는 다음과 같은 도구가 포함되어 있습니다.

- Vitis Embedded - 내장형 Arm 프로세서에서 실행되는 C/C++ 애플리케이션 코드 개발

- 컴파일러 및 시뮬레이터 - AI 엔진 어레이를 사용한 설계 구현

- Vitis HLS - FPGA 패브릭을 대상으로 하는 C/C++ 기반 IP 블록 개발

- Vitis Model Composer - MathWorks Simulink® 환경에서 신속한 설계 탐색을 지원하는 모델 기반 설계 도구

- FPGA 패브릭 또는 AI 엔진에서 구현 가능한 성능 최적화된 오픈 소스 기능(예: DSP, Vision, Solver, 초음파, BLAS 등)

도구 및 라이브러리

Vitis Embedded

Vitis™ Embedded는 내장형 Arm 프로세서에서 실행되는 호스트 애플리케이션 개발을 위한 독립형 내장형 소프트웨어 개발 패키지입니다.

Vitis AIE DSP 설계 도구

컴파일러 및 시뮬레이터

AMD Versal™ ACAP(Adaptive SoC) 디바이스는 리소스 및 전력을 최적화하여 고성능 DSP 기능을 구현할 수 있는 AI 엔진 어레이를 갖추고 있습니다. AI 엔진을 FPGA 패브릭 리소스와 함께 사용하면 고성능 DSP 애플리케이션을 매우 효율적으로 구현할 수 있습니다.

Vitis HLS

Vitis HLS 도구를 사용하면 C/C++ 함수를 RTL로 합성하여 복잡한 FPGA 알고리즘을 쉽게 만들 수 있습니다.

Vitis HLS 도구는 합성 및 배치/경로를 위한 Vivado™ Design Suite, 이종 시스템 설계 및 애플리케이션을 위한 Vitis 통합 소프트웨어 플랫폼과 긴밀하게 통합되어 있습니다.

Vitis 모델 컴포저

Vitis Model Composer는 MathWorks Simulink® 환경에서 신속한 설계 탐색을 지원하는 모델 기반 설계 도구입니다.

또한 이 도구를 사용하면 AI 엔진과 프로그래밍 가능한 로직(HDL/HLS) 블록을 혼합하여 설계를 모델링하고 시뮬레이션할 수 있습니다.

Vitis 라이브러리

C, C++로 작성된 기존 애플리케이션에 대한 코드 변경을 최소화하거나 코드 변경을 수행하지 않고 즉시 사용 가능한 가속화 기능을 제공하는 성능 최적화된 오픈 소스 라이브러리입니다.

도메인별 가속 라이브러리를 그대로 활용하거나, 요구 사항에 맞게 수정하거나, 맞춤형 가속기에서 알고리즘 빌딩 블록으로 사용할 수 있습니다.

도구 사용

AMD ACAP(Adaptive SoC) 및 FPGA의 다른 부분을 구축하려면 서로 다른 Vitis 도구를 사용해야 합니다.

| FPGA(프로그래밍 가능 로직) | 처리 하위 시스템 | AI 엔진 |

|---|---|---|

| Vivado Design Suite / Vitis HLS / Vitis 모델 컴포저 | Vitis Embedded | AIE 컴파일러 및 시뮬레이터 / Vitis 모델 컴포저 |

설계 흐름

Vitis Embedded 소프트웨어 개발 흐름

(기존에는 이전 FPGA 제품군에서 내장형 SDK라고 함)

Vivado에서 플랫폼 파일로 하드웨어 내보내기 |

애플리케이션 코드 개발

|

부팅 이미지 디버깅 및 생성 |

AMD ACAP(Adaptive SoC)에서 Arm® 내장형 프로세서 하위 시스템용 C/C++ 코드를 개발하는 설계자가 일반적으로 이 흐름을 사용합니다.

- 하드웨어 엔지니어는 프로그래밍 가능한 로직을 설계하고 AMD Vivado™ Design Suite를 사용하여 하드웨어를 XSA(Xilinx Support Archive) 파일로 내보냅니다.

- 소프트웨어 엔지니어는 이러한 하드웨어 설계 정보를 대상 플랫폼에 통합하고 Vitis Embedded 소프트웨어를 사용하여 애플리케이션 코드를 개발합니다.

개발자는 애플리케이션을 실행하기 위해 Vitis Embedded 소프트웨어 내에서 모든 시스템 수준 검증을 수행하고 부팅 이미지를 생성할 수 있습니다.

Vitis 소프트웨어 플랫폼을 사용한 임베디드 소프트웨어 애플리케이션 개발 워크플로에 대한 자세한 내용은 사용자 가이드(UG1400)의 내장형 소프트웨어 개발용 Vitis 도구 섹션을 참조하세요.

Vitis 시스템 설계 흐름

(하드웨어 및 소프트웨어)

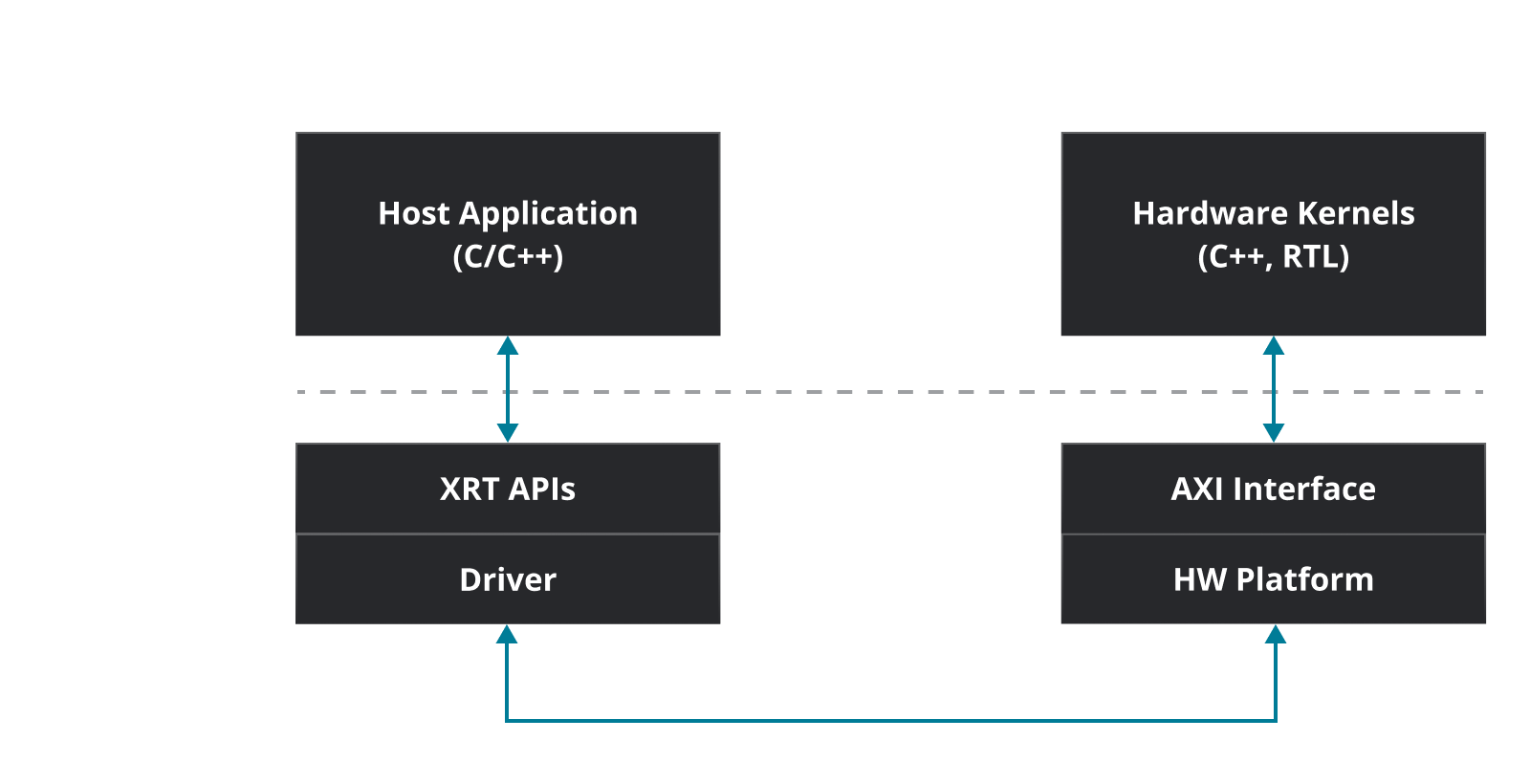

AMD ACAP(Adaptive SoC)에 설계의 소프트웨어 및 하드웨어 부분을 통합하는 시스템 설계자가 일반적으로 이러한 흐름을 사용합니다.

이 흐름은 Arm® 내장형 프로세서에서 실행되는 소프트웨어 애플리케이션과 PL(Programmable Logic) 및/또는 Versal™ AI Engine 어레이에서 실행되는 컴퓨팅 커널로 구성된 이종 내장형 시스템 설계를 개발하는 데 사용됩니다.

이 흐름은 다음과 같이 구성되어 있습니다.

- C/C++로 작성되어 일반적으로 내장형 Arm 프로세서 하위 시스템에서 실행되는 소프트웨어 호스트 애플리케이션. AMD Vitis 런타임 라이브러리에서 구현된 네이티브 API를 사용하여 AMD 디바이스 내의 하드웨어 커널과 통신합니다.

- AMD Vitis™ HLS 도구를 사용하여 C++에서 생성하거나 AMD Vivado™ Design Suite를 사용하여 RTL에 직접 설명을 제공할 수 있는 하드웨어 커널.

Vitis 통합 소프트웨어 플랫폼을 사용한 이종 시스템 설계 흐름에 대한 자세한 내용은 사용자 가이드(UG1393)의 이종 시스템 설계용 Vitis 도구 섹션을 참조하세요.

AMD Alveo™ Data Center 가속기 카드는 동일한 시스템 설계 흐름을 사용합니다. 따라서 소프트웨어 프로그램은 x86 호스트에서 실행되고 커널은 PCIe® 연결 가속화 카드의 FPGA에서 실행됩니다. Vitis 통합 소프트웨어 플랫폼을 사용한 데이터 센터 가속화 흐름에 대한 자세한 내용은 사용자 가이드(UG1393)의 데이터 센터 가속화용 Vitis 도구 섹션을 참조하세요.

2024.2의 새로운 기능

AMD Versal™ AI Engine DSP 설계를 위한 개선 사항

- Vitis Analyzer를 사용한 지연 시간 및 처리량 추산

- Vitis Analyzer를 사용하여 사용할 수 없는 PLIO 표시

- 힙 스택 및 프로그램 메모리 보고

- Versal AI Engine 설계의 신속한 프로토타이핑을 위한 새로운 흐름

AI 엔진을 위한 향상된 새로운 Vitis 라이브러리 기능

- AIE를 사용하는 Versal AI Core 시리즈를 위한 향상된 DSP 라이브러리 기능: TDM FIR 필터링, 고성능 GEMM/GEMV, 2D IFFT

- AIE-ML을 사용하는 Versal AI Edge 시리즈를 위한 새로운 DSP 라이브러리 기능: TDM FIR 필터링, Radix-3/Radix-5 FFT 지원, GEMM/GEMV

AMD Vitis IDE의 주요 개선 사항(새로운 GUI)

- 새 직렬 터미널: 하드웨어의 직렬 메시지 모니터링

- 확장 기능 마켓플레이스 - 타사 확장 기능 설치 및 탐색

- PS 트레이스 - 내장형 시스템의 성능을 디버깅하고 최적화하는 새로운 기능

자세한 내용은 새로운 기능 및 AMD Vitis IDE 페이지를 참조하세요.