概要

ホスト接続を高速化

統合型 PCIe® Gen6 および CXL® 3.11 を備えた、FPGA 業界初のアダプティブ SoC & FPGA は、同等クラスの FPGA と比較して 2 倍のレーンあたり帯域幅を実現します。2

より多くのメモリを迅速に実現

最大 8533 Mb/s の LPDDR5X、最大 6400 Mb/s の DDR5、最大 64 Gb/s の CXL メモリ拡張モジュールをサポートするハード実装されたメモリ コントローラーにより、外部メモリ帯域幅を倍増させることができます。3、4

データ セキュリティの強化

ハード IP、ハード インライン ECC、および外部メモリ向け暗号化における統合 PCIe の整合性およびデータ暗号化 (IDE) のサポートにより、転送中や保存中のデータを保護します。

業界をリードする広帯域幅ホスト接続機能を活用

AMD Versal™ プレミアム シリーズ Gen 2 は、PCIe Gen6 およびハード IP で 64 Gb/s の CXL 3.1 に対するサポートを提供する、業界初の FPGA (アダプティブ SoC) です。システム全体のスループットとリソース使用率を向上させ、データを多用するアプリケーションのニーズに対応できます。1

動的割り当てメモリ プーリングでより多くのメモリ リソースにアクセス

メモリのボトルネックを削減し、データ フローをスピードアップして、データを多用するアプリケーションを加速し、価値あるインサイトを明らかにできます。Versal プレミアム シリーズ Gen 2 アダプティブ SoC は、より多くのメモリを迅速に実現し、システム全体のスループットを向上させます。その 5 つの方法をご紹介します。

製品の特長

Versal プレミアム シリーズ Gen 2 の紹介

AMD Versal プレミアム シリーズ アダプティブ SoC 機能を拡張した Versal プレミアム シリーズ Gen 2 が提供する新しいインターフェイス機能には、強化されたトランシーバー アーキテクチャ、PCIe Gen6 CXL 3.1、LPDDR5X、DDR5 のサポートが含まれ、データを多用する将来のアプリケーションの要件に対応できるよう調整されています。

デバイス/パッケージの各組み合わせで利用可能な機能については、データシートの概要を参照してください。

主な特長

強化されたトランシーバー アーキテクチャ

Versal プレミアム シリーズ Gen 2 アダプティブ SoCs 機能は新しいトランシーバー アーキテクチャを備え、NRZ および PAM4 モードで動作し、1.25 Gb/s ~ 128 Gb/s の高速データ転送速度を提供します。5 PCIe Gen5 および 100G/600G イーサネット コアに加え、Versal プレミアム シリーズ Gen 2 アダプティブ SoC はメモリ コヒーレントなプロセッサ インターフェイスを提供する CXL 3.1 と、PCIe Gen5 に比べ 2 倍のチャネルあたり帯域幅をもたらす PCIe Gen6 のサポートを提供します。2

DDR5 & LPDDR5X

ハード DDR メモリ コントローラーは、DDR5 を最大 6400 Mb/s、LPDDR5X を最大 8533 Mb/s でサポートし、新たなインライン ECC と暗号化機能を備え、最大 273 GB/s のメモリ帯域幅をもたらします。

安全性機能およびセキュリティ機能

転送中のデータは PCIe 整合性およびデータ暗号化 (IDE) で保護し、保存中のデータは専用メモリ コントローラーに内蔵されたインライン メモリ暗号化で保護し、400G 高速暗号化エンジンは広帯域幅インターフェイス向けに最大 800 Gb/s のライン レート暗号化スループットでデータを保護します。

FEC 機能付きマルチレート イーサネット コア

専用のコネクティビティ IP により、幅広いデータ レートとプロトコルをサポートするセキュアなテラビット単位のイーサネットを実現できます。100G イーサネット コアと 600G イーサネット コアを組み合わせることで、最大 3.1 Tb/s のスループットを実現でき、クラウドとエッジのスケーラビリティにすべて単一のプラットフォームで対応できます。

プログラマブル ロジックと I/O

Versal アーキテクチャのプログラマブル ロジックと、MIPI D-PHY を最大 4.5 Gb/s、C-PHY を最大 10 Gb/s でサポートする新しいハイパフォーマンス X5IO は、柔軟性、リアルタイム処理、および将来的な適応性を提供します。

プログラム可能なネットワーク オン チップ

プログラム可能なネットワーク オン チップ (NoC) は、Versal アダプティブ SoC アーキテクチャ内の演算エンジンと統合 IP ブロック間に最適化済みのテラビット単位のインターコネクトを提供します。これにより、タイミング クロージャが容易になり、ロジック リソースも節約できます。NoC コンパイラは合理的なプログラミング フローを提供し、ユーザーが重要なデータパスのレイテンシと QoS を管理できるようになります。

その他の Versal アダプティブ SoC の機能

Versal プレミアム シリーズ Gen 2 製品概要

Versal プレミアム シリーズ Gen 2 アダプティブ SoC は、将来のデータ、および帯域幅を非常に多用するアプリケーションに対応する高度な接続性とセキュリティ ソリューションにより、データの価値を大規模に引き出すソリューションを実現します。

アプリケーションと業界

データセンター ストレージ アプリケーション向け AMD Versal プレミアム シリーズ Gen 2 アダプティブ SoC

Versal プレミアム シリーズ Gen 2 デバイスは、カスタム エンタープライズ SSD、暗号化/圧縮アクセラレータ、メモリ プーリング、ライブ移行など、データセンターの幅広いストレージ アプリケーションに最適です。Versal プレミアム シリーズ Gen 2 に CXL 3.1 が加わったことで、メモリ拡張を追加し、演算タスクをメモリに近づけることができるため、最もメモリ負荷の高い要件にも対応できます。

航空宇宙および防衛アプリケーションにおける SWaP に最適化された演算向け AMD Versal プレミアム シリーズ Gen 2

Versal プレミアム シリーズ Gen 2 は、実証済みの Versal プレミアム シリーズ アダプティブ SoC を拡張し、高集積度演算、より広いメモリ帯域幅、アップグレードされた I/O & GT、強化されたセキュリティ機能を備えています。そのすべてをスモール フォーム ファクター システムに対して最適化し、4000 を超える DSP58 ブロックを 1 つの 35x35 mm パッケージに集約し、7500 を超える DSP58 ブロックを 1 つの 3U VPX 互換性パッケージに集約しています。

AMD Versal プレミアム シリーズ Gen 2 を備えた MIPI C-PHY/D-PHY テスト ソリューション

強化された MIPI C-PHY/D-PHY シリコン製品と、対応する CSI および DSI ソリューションを備えた Versal プレミアム シリーズ Gen 2 は、ディスプレイおよびカメラのテストにおける新しい接続規格をサポートします。

次世代の計測装置要件を満たす AMD Versal プレミアム シリーズ Gen 2

次世代テスト装置は、新しい規格や大きな I/O およびメモリ帯域幅をサポートするために、強化された SerDes 機能が必要です。Versal プレミアム シリーズ Gen 2 は、SerDes の改善や高スループットの PCIe および DMA 機能により、そのような要件を満たします。

製品仕様

プロセッシング システム

2VP3102 |

2VP3202 |

2VP3402 |

2VP3602 |

|

アプリケーション プロセッサ |

デュアル コア Arm® Cortex® A72、48 KB/32 KB L1 キャッシュ (パリティおよび ECC 付き)、1 MB L2 キャッシュ (ECC 付き) |

|||

リアルタイム プロセッサ |

デュアル コア Arm Cortex R5F、32 KB/32 KB L1 キャシュ、および 256 KB TCM (ECC 付き) |

|||

メモリ |

256 KB オンチップ メモリ (ECC 付き) |

|||

接続性 |

Ethernet (x2)、UART (x2)、CAN-FD (x2)、USB 2.0 (x1)、SPI (x2)、I2C (x2) |

|||

プログラマブル ロジック

2VP3102 |

2VP3202 |

2VP3402 |

2VP3602 |

|

システム ロジック セル |

1,407,560 |

1,743,560 |

2,561,160 |

3,273,480 |

LUT 数 |

643,456 |

797,056 |

1,170,816 |

1,496,448 |

DSP エンジン |

3,332 |

4,004 |

6,080 |

7,616 |

メモリ、インターフェイス、I/O、トランシーバー

2VP3102 |

2VP3202 |

2VP3402 |

2VP3602 |

|

総 PL メモリ1 (Mb) |

145 |

178 |

256 |

327 |

最大メモリ帯域幅 (LPDDR5X) |

137 GB/s |

137 GB/s |

273 GB/s |

273 GB/s |

100G マルチレート イーサネット MAC |

2 |

2 |

1 |

1 |

600G Ethernet MAC |

1 |

2 |

3 |

5 |

400G 高速暗号化エンジン |

2 |

2 |

1 |

1 |

LDPC デコーダー |

4 |

6 |

- |

- |

DMA 内蔵 PCIe®、CXL (CPM6) |

2 x Gen6x8/CXL 3.1 |

2 x Gen6x8/CXL 3.1 |

2 x Gen6x8/CXL 3.1 |

2 x Gen6x8/CXL 3.1 |

高性能 I/O (X5IO) |

416 |

416 |

736 |

736 |

GTM2 トランシーバー (PL のみ – 112 G3、56G) |

8、8 |

8、8 |

40、0 |

56、0 |

GTM2 トランシーバー (CPM6/GT Direct モード – 64G/32G)2 |

16 |

16 |

16 |

16 |

- * 総 PL メモリ = 分散 RAM + 総ブロック RAM + UltraRAM

- CPM6 モードで最大 64G。GT Direct モードで最大 32G

- 128Gb/s サポートの詳細については AMD に問い合わせください

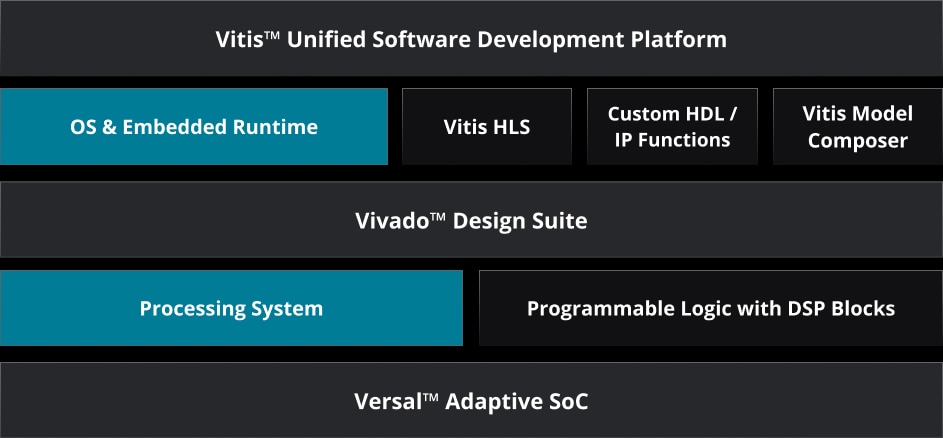

すべての開発者向け

AMD は、アダプティブ SoC および FPGA を使用した設計をサポートする、業界をリードするソフトウェア開発環境を提供しています。これには、ツール (コンパイラ、シミュレータなど)、IP、およびソリューションが含まれます。

この環境を利用することで、ワットあたりの性能が高いデザインを短期間に構築できます。これらのツールは、AI サイエンティストから、アプリケーション エンジニア、アルゴリズム エンジニア、エンベデッド ソフトウェア開発者、従来のハードウェア開発者に至るまで、あらゆる開発者が AMD アダプティブ コンピューティング ソリューションを最大限に活用できるようサポートします。

リソース

アーリー アクセス プログラム

Versal AI エッジ シリーズ Gen 2 は、現在アーリー アクセスで提供されています。アーリー アクセス プログラムについては、AMD の販売代理店へお問い合わせいただくか、"営業に問い合わせ" ページをご利用ください。

最新情報を入手

Versal アダプティブ SoC 通知リストに登録された方には、最新情報をいち早くお届けします。

脚注

- 2024 年 7 月時点での AMD の社内分析に基づいています。AMD Versal プレミアム シリーズ Gen 2 デバイス (CXL 3.1 および PCIe6.0 対応) と、CXL 3.1 非対応および/または PCIe Gen4/5 を搭載した競合デバイスを比較しています。(VER-055)

- 2024 年 7 月時点での AMD の社内分析に基づいています。PCIe Gen6 対応の AMD Versal プレミアム シリーズ Gen 2 デバイスと、PCIe Gen4/5 対応の競合デバイスおよび前世代の Versal プレミアム シリーズのデバイスを比較しています。実際のライン レート速度は、システム構成やその他の要因によって異なる可能性があります。 (VER-057)

- 2024 年 7 月時点での AMD の社内分析に基づいています。Versal プレミアム シリーズ Gen 2 デバイスの DDR/LPDDR メモリ インターフェイス仕様と同等の競合デバイスを比較しています。実際の性能は、システム構成やその他の要因によって異なる可能性があります。(VER-058)

- AMD の社内分析結果に基づいています。AMD Versal プレミアム シリーズ Gen 2 デバイスで、CXL 3.1 および LPDDR5X メモリ コンポーネントを使用した場合と、LPDDR5X メモリのみを使用した場合の総メモリ帯域幅を比較しています。メモリ帯域幅は、システム構成やその他の要因によって異なる可能性があります。(VER-059)

- データは暫定的であり、変動する可能性があります(VER-063)

- 2024 年 7 月時点での AMD の社内分析に基づいています。AMD Versal プレミアム シリーズ Gen 2 デバイス (CXL 3.1 および PCIe6.0 対応) と、CXL 3.1 非対応および/または PCIe Gen4/5 を搭載した競合デバイスを比較しています。(VER-055)

- 2024 年 7 月時点での AMD の社内分析に基づいています。PCIe Gen6 対応の AMD Versal プレミアム シリーズ Gen 2 デバイスと、PCIe Gen4/5 対応の競合デバイスおよび前世代の Versal プレミアム シリーズのデバイスを比較しています。実際のライン レート速度は、システム構成やその他の要因によって異なる可能性があります。 (VER-057)

- 2024 年 7 月時点での AMD の社内分析に基づいています。Versal プレミアム シリーズ Gen 2 デバイスの DDR/LPDDR メモリ インターフェイス仕様と同等の競合デバイスを比較しています。実際の性能は、システム構成やその他の要因によって異なる可能性があります。(VER-058)

- AMD の社内分析結果に基づいています。AMD Versal プレミアム シリーズ Gen 2 デバイスで、CXL 3.1 および LPDDR5X メモリ コンポーネントを使用した場合と、LPDDR5X メモリのみを使用した場合の総メモリ帯域幅を比較しています。メモリ帯域幅は、システム構成やその他の要因によって異なる可能性があります。(VER-059)

- データは暫定的であり、変動する可能性があります(VER-063)